GR740-UM-DS, Nov 2017, Version 1.7 283 www.cobham.com/gaisler

GR740

ted master that initiated the transfer is allowed in bus arbitration by asserting the HSPLIT signal to the

AHB controller. The first access in the transfer is completed by returning read data. The next access in

the transfer on the slave side is extended by asserting HREADY low. On the master side the next

access is started by performing a SEQ transfer (and then holding the bus using BUSY transfers). This

sequence is repeated until the transfer is ended on the slave side.

In case of an ERROR response on the master side the ERROR response will be given for the same

access (address) on the slave side. SPLIT and RETRY responses on the master side are re-attempted

until an OKAY or ERROR response is received.

18.2.3 AHB write transfers

The AHB/AHB bridge implements posted writes. During the AHB write transfer on the slave side the

data is buffered in the internal write FIFO and the transfer is completed on the slave side by always

giving an OKAY response. The master interface requests the bus and performs the write transfer when

the master bus is granted.

Writes are accepted with zero wait states if the bridge is idle and the incoming access is not locked. If

the incoming access is locked, each access will have one wait state.

18.2.4 Locked transfers

The AHB/AHB bridge supports locked transfers. When a locked transfer is made from the Processor

AHB bus, the Slave I/O AHB bus will be locked when the bus is granted and remain locked until the

transfer completes on the Processor AHB side.

Locked transfers can lead to deadlock conditions when a locked transfer is made after a read access

that has received a SPLIT response from the bridge. The AMBA specification requires that the locked

transfer is handled before the previous transfer, which received a SPLIT response, is completed. The

bridge will avoid the deadlock condition by saving state for the read access that received a SPLIT

response, allow the locked access to complete, and then complete the first access. All non-locked

accesses from other masters will receive SPLIT responses until the saved data has been read out.

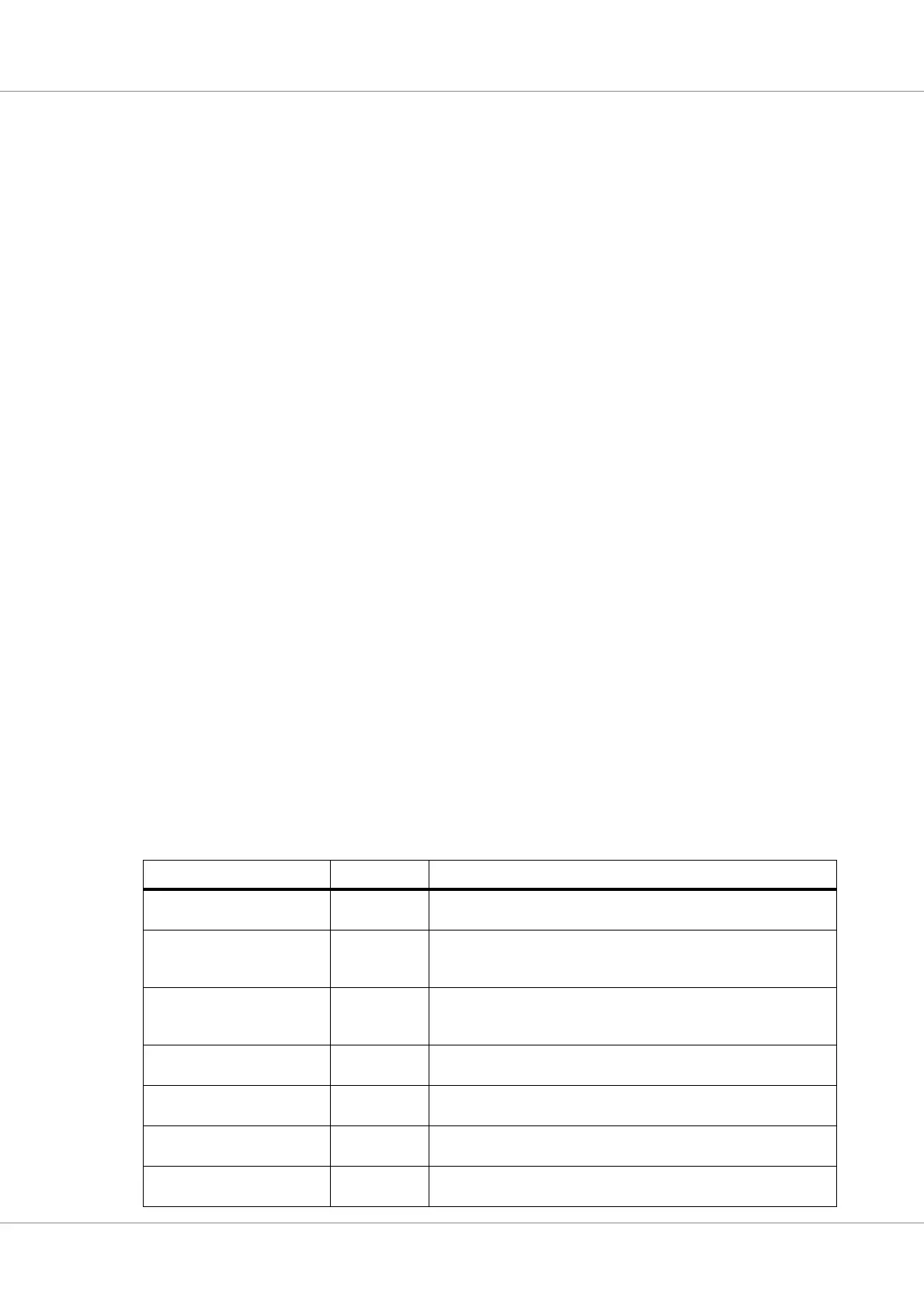

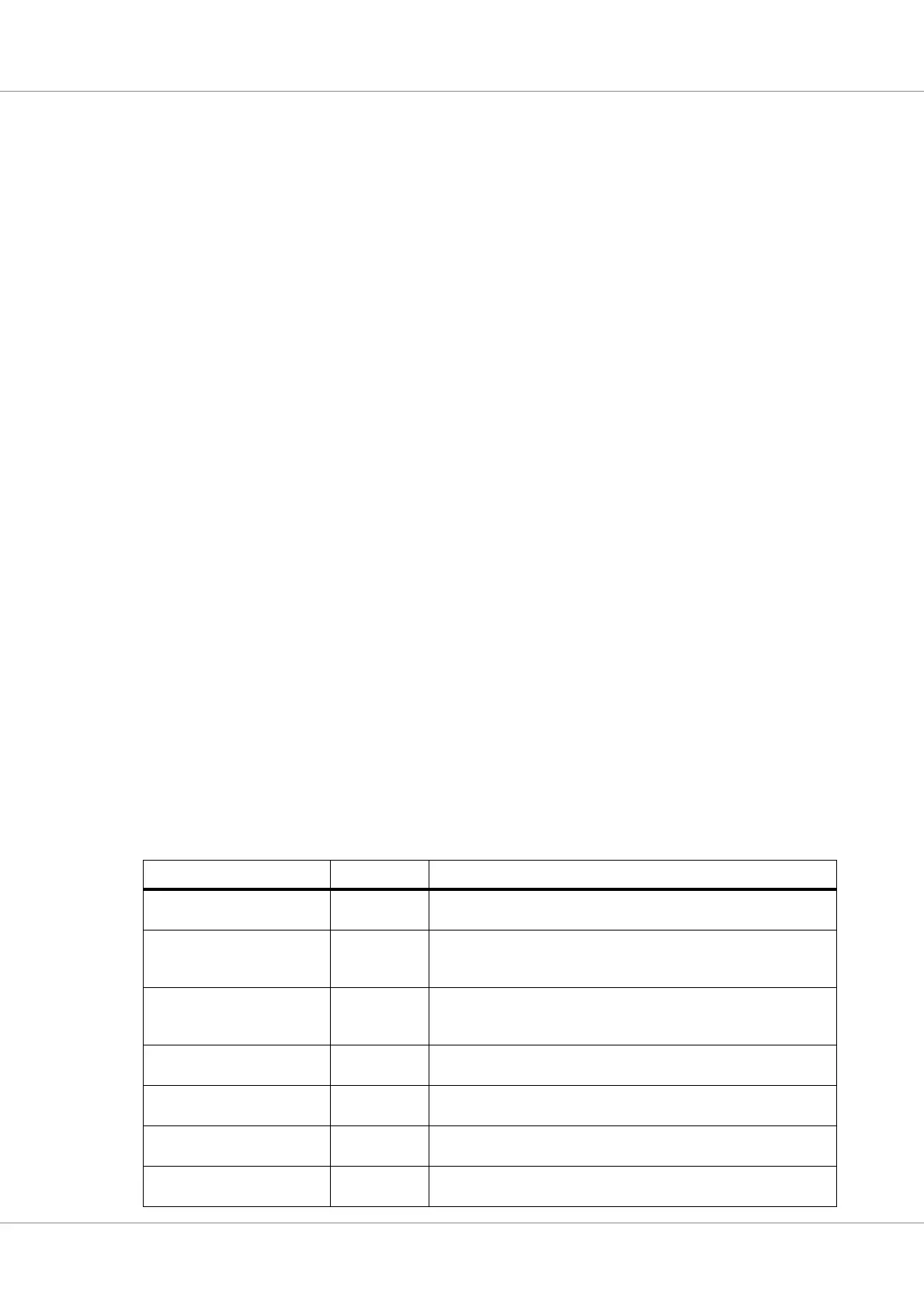

18.2.5 Read and write combining

Read and write combining allows the bridge to assemble or split AMBA accesses on the bridge’s

slave interface into one or several accesses on the master interface. The table below shows the effect

of read and write combining on incoming access from the Processor AHB bus.

Table 361.Read and write combining

Access on slave interface Access size Resulting access(es) on master interface

BYTE or HALF-WORD single

read access to any area

- Single access of same size

BYTE or HALF-WORD read

burst to prefetchable area

- Incremental read burst of same access size as on slave interface, the

length is the same as the number of 32-bit words in the read buffer, but

will not cross the read burst boundary.

BYTE or HALF-WORD read

burst to non-prefetchable area

- Incremental read burst of same access size as on slave interface, the

length is the same as the length of the incoming burst. The master

interface will insert BUSY cycles between the sequential accesses.

BYTE or HALF-WORD single

write

- Single access of same size

BYTE or HALF-WORD write

burst

- Incremental write burst of same size and length, the maximum length

is the number of 32-bit words in the write FIFO.

Single read access to any area Access size <=

32-bits

Single access of same size

Single read access to any area Access size >

32-bits

Burst of 32-bit accesses. Length of burst: (access size)/(32 bits)

Loading...

Loading...