GR740-UM-DS, Nov 2017, Version 1.7 83 www.cobham.com/gaisler

GR740

Arithmetic operations include addition, subtraction, multiplication, division and square-root. Each

arithmetic operation can be performed in single or double precision formats. Arithmetic operations

have one clock cycle throughput and a latency of four clock cycles, except for divide and square-root

operations, which have a throughput of 16 - 25 clock cycles and latency of 16 - 25 clock cycles (see

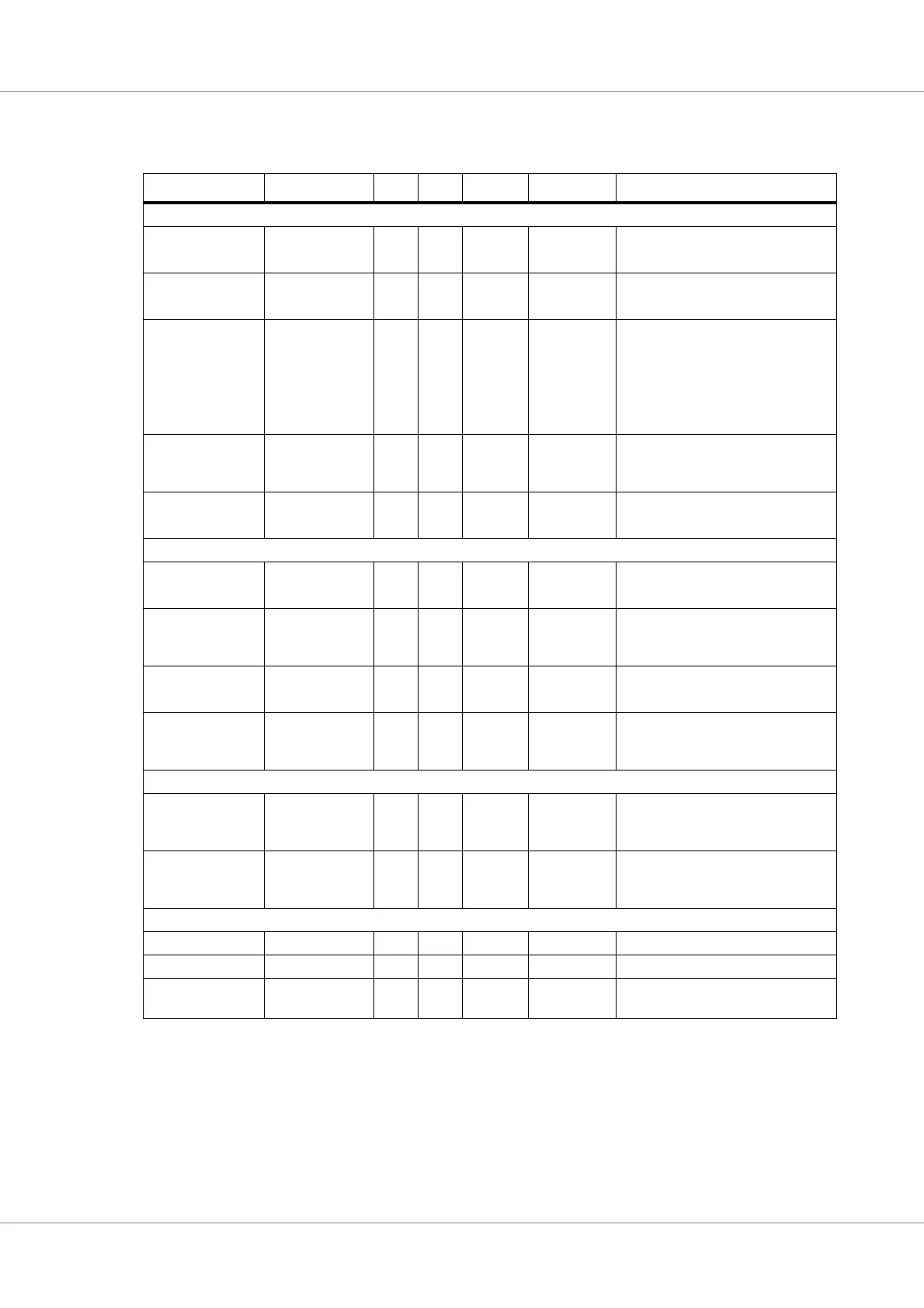

Table 62. : GRFPU operations

Operation OpCode[8:0] Op1 Op2 Result Exceptions Description

Arithmetic operations

FADDS

FADDD

001000001

001000010

SP

DP

SP

DP

SP

DP

UNF, NV,

OF, UF, NX

Addition

FSUBS

FSUBD

001000101

001000110

SP

DP

SP

DP

SP

DP

UNF, NV,

OF, UF, NX

Subtraction

FMULS

FMULD

FSMULD

001001001

001001010

001101001

SP

DP

SP

SP

DP

SP

SP

DP

DP

UNF, NV,

OF, UF, NX

UNF, NV,

OF, UF, NX

UNF, NV,

OF, UF

Multiplication, FSMULD gives

exact double-precision product of

two single-precision operands.

FDIVS

FDIVD

001001101

001001110

SP

DP

SP

DP

SP

DP

UNF, NV,

OF, UF, NX,

DZ

Division

FSQRTS

FSQRTD

000101001

000101010

-

-

SP

DP

SP

DP

UNF, NV,

NX

Square-root

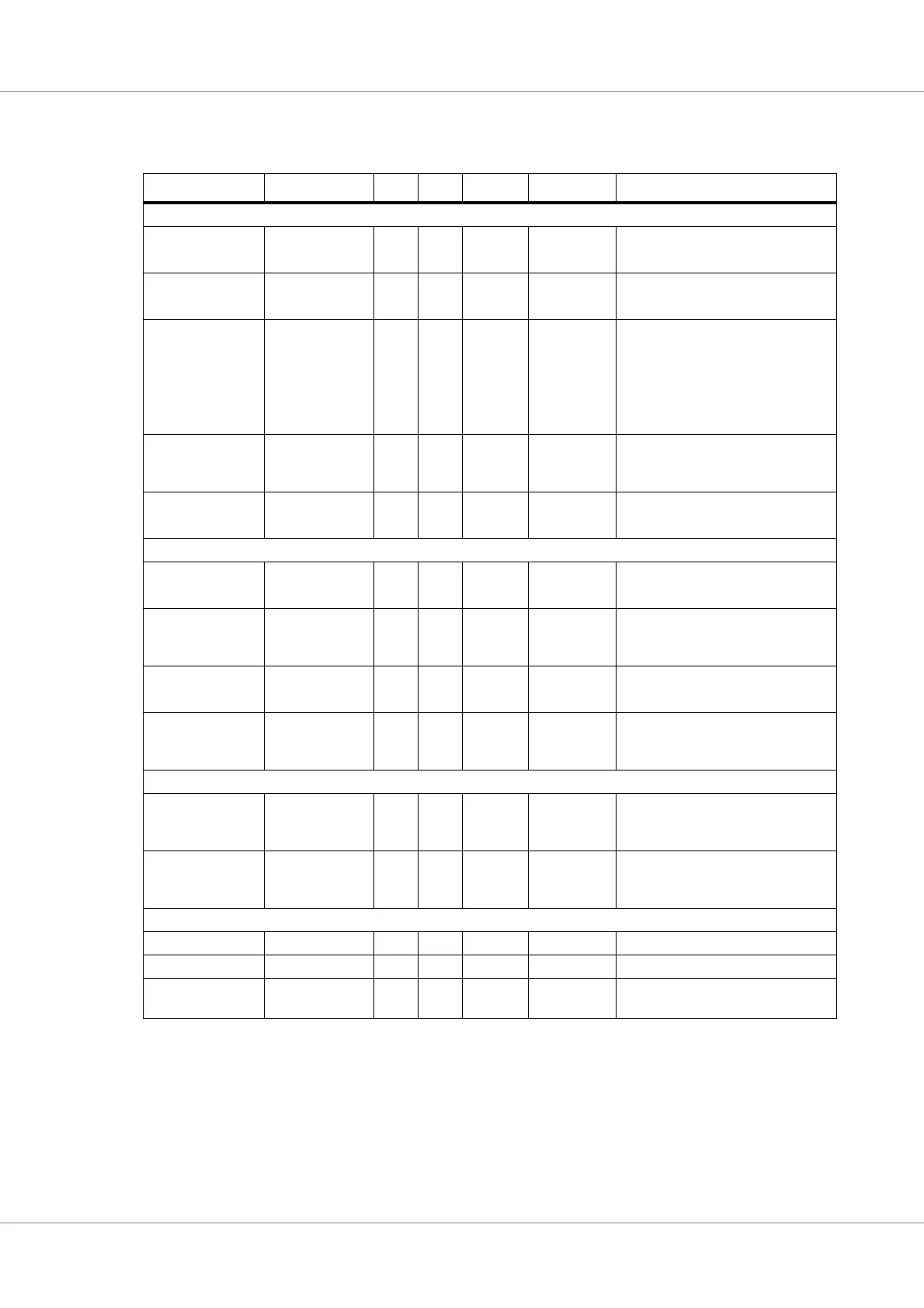

Conversion operations

FITOS

FITOD

011000100

011001000

-INTSP

DP

NX

-

Integer to floating-point conversion

FSTOI

FDTOI

011010001

011010010

-SP

DP

INT UNF, NV,

NX

Floating-point to integer conversion.

The result is rounded in round-to-

zero mode.

FSTOI_RND

FDTOI_RND

111010001

111010010

-SP

DP

INT UNF, NV,

NX

Floating-point to integer conversion.

Rounding according to RND input.

FSTOD

FDTOS

011001001

011000110

-SP

DP

DP

SP

UNF, NV

UNF, NV,

OF, UF, NX

Conversion between floating-point

formats

Comparison operations

FCMPS

FCMPD

001010001

001010010

SP

DP

SP

DP

CC NV Floating-point compare. Invalid

exception is generated if either oper-

and is a signaling NaN.

FCMPES

FCMPED

001010101

001010110

SP

DP

SP

DP

CC NV Floating point compare. Invalid

exception is generated if either oper-

and is a NaN (quiet or signaling).

Negate, Absolute value and Move

FABSS 000001001 - SP SP - Absolute value.

FNEGS 000000101 - SP SP - Negate.

FMOVS 000000001 SP SP - Move. Copies operand to result out-

put.

SP - single precision floating-point number

DP - double precision floating-point number

CC - condition codes INT - 32 bit integer

UNF, NV, OF, UF, NX - floating-point exceptions, see section 8.2.3

Loading...

Loading...