GR740-UM-DS, Nov 2017, Version 1.7 99 www.cobham.com/gaisler

GR740

9.4.13 Error Handling / Injection configuration

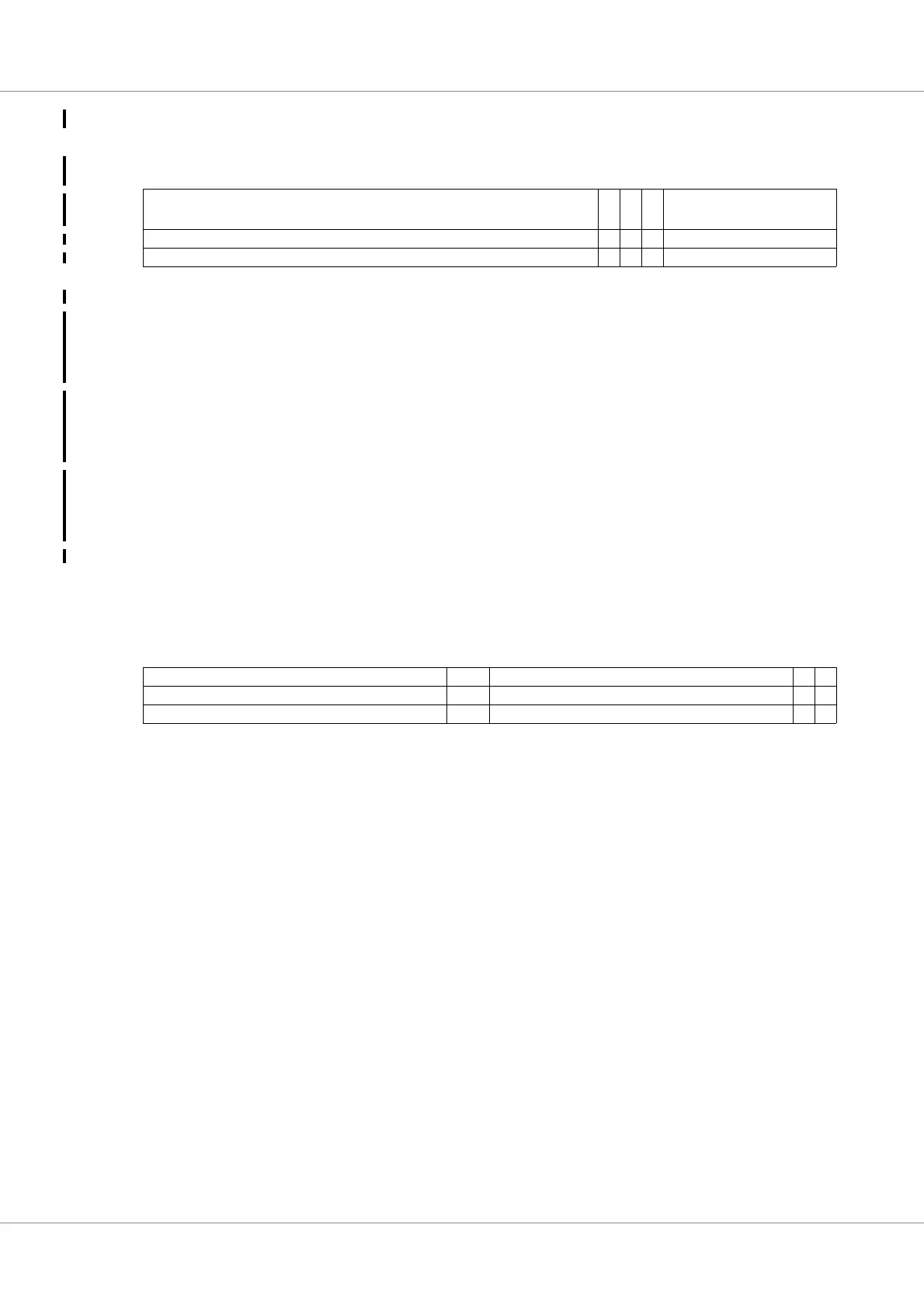

Table 81. 0x4C - L2CEINJCFG - L2C injection configuration register

(only available in revision 1)

9.4.14

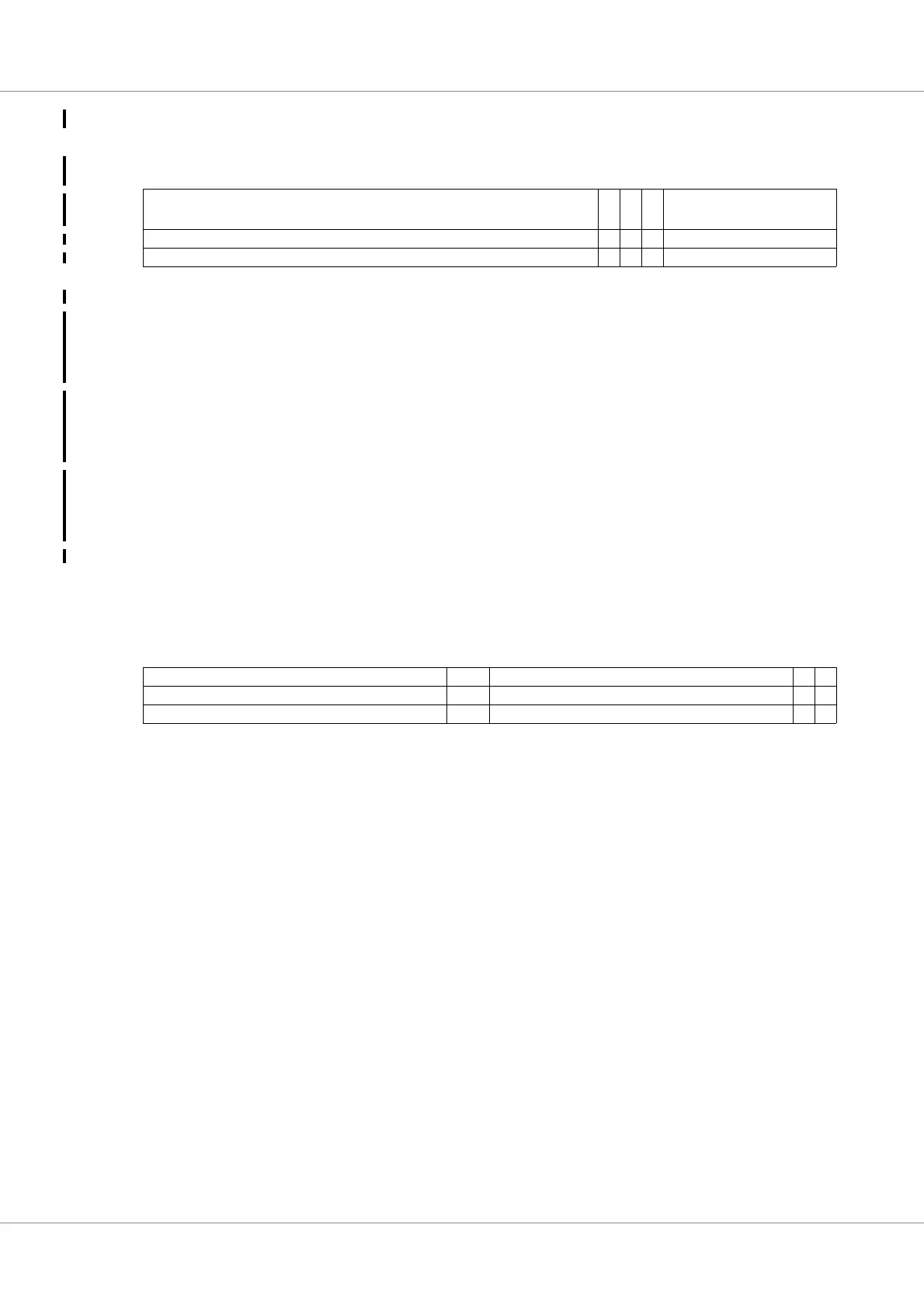

Table 82. 0x80-FC - L2CMTRR - L2C Memory type range register

Memory type range registers

31 11 10 9 8 7 0

RESERVED E

D

I

T

E

R

I

M

D

RES

00000

rrwrwrwr

31: 11 RESERVED

10 (EDI) - Enable invalidation off cache line with un-correctable data error.

When set to 1 and a un-correctable data error is detected, the cache line will be invalidated (remov-

ing the error form the cache).

.This field is only available in silicon revision 1.

9 (TER) - Disable error response on un-correctable TAG error detection.

When set to 0 the access detecting a un-correctable TAG error would generate a AMBA error

response. When set to 1 this access would not generate an error response.

This field is only available in silicon revision 1.

8 (IMD) - Disable index match only after un-correctable TAG error.

When set to 1 the TAG and INDEX are matched against the error address register after a detected un-

correctable TAG error. When set to 0 only the INDEX are matched against the error address register.

This field is only available in silicon revision 1

7: 0 RESERVED

31 18 17 16 15 2 1 0

ADDR ACC MASK WP AC

00000

rw rw rw rw rw

31: 18 Address field (ADDR) - to be compared to the cache address [31:18]

17: 16 Access field (ACC) - 00: uncached, 01: write-through

15: 2 Address mask (MASK) - Only bits set to 1 will be used during address comparison

1 Write-protection (WP) - 0: disabled, 1: enabled

0 Access control field (AC) -. 0: disabled, 1: enabled

Loading...

Loading...