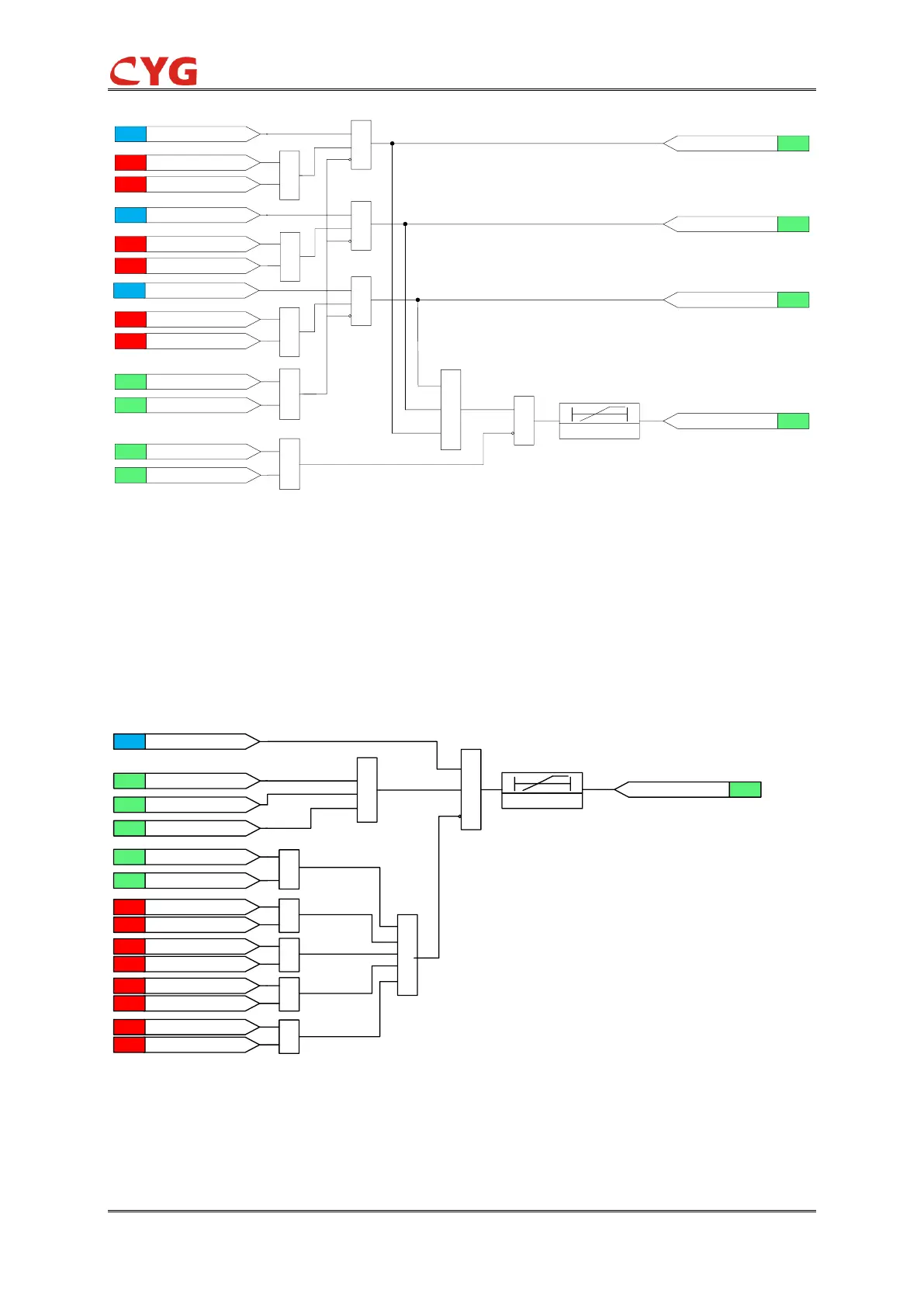

Figure 3.23-1 Logic Diagram of Dead charge check logic

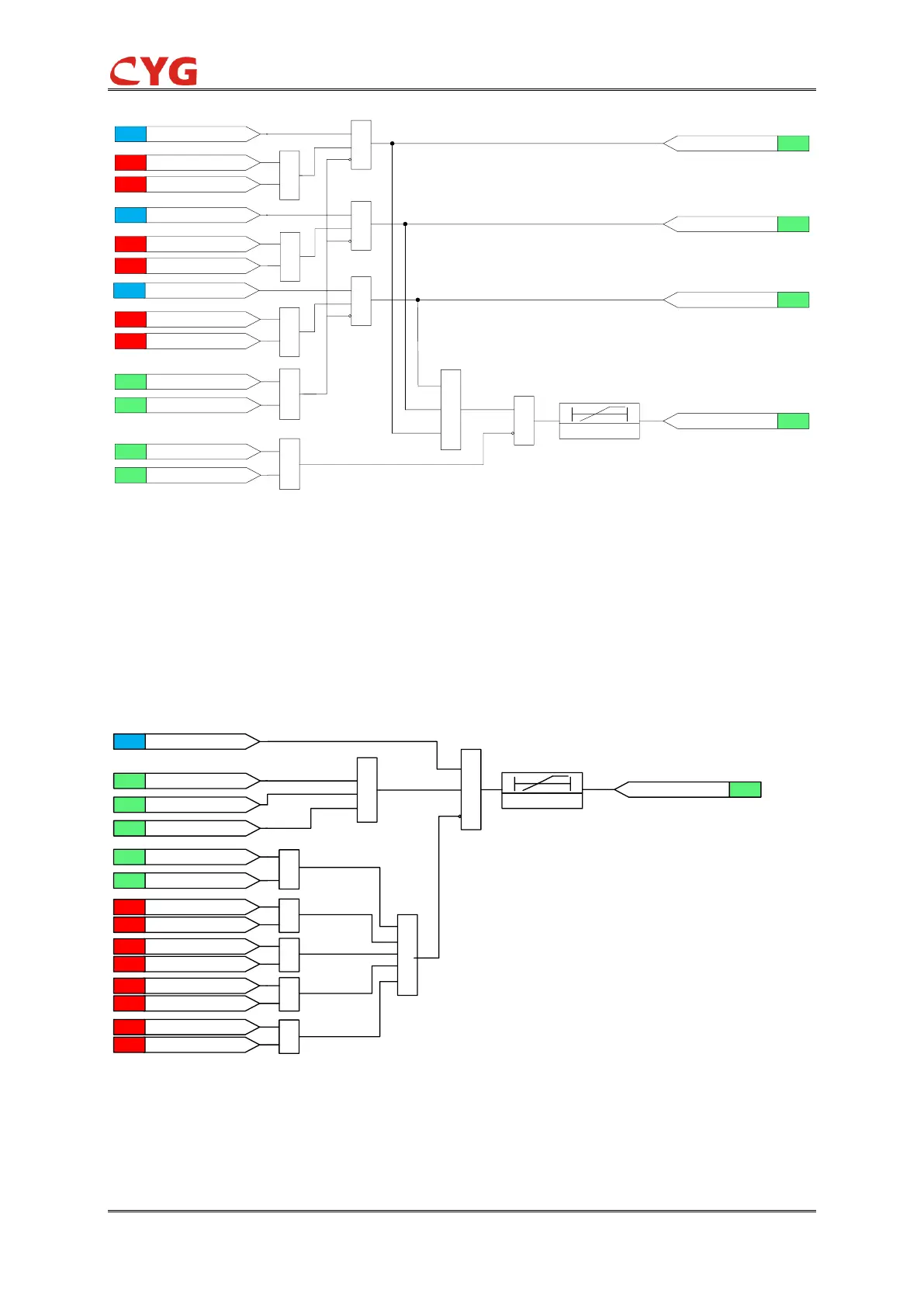

The frequency difference, voltage difference, and phase difference of voltages from both sides of

the circuit breaker are calculated in the device, they are used as input conditions of the

synchronism check. When the synchronism check function is enabled and the voltages of both

ends meet the requirements of the voltage difference, phase difference, and frequency difference,

and there is no synchronism check blocking signal, and the measured bus voltage and line voltage

for synchro-check should not exceed the overvoltage threshold 25SYN_OV or lag the under

voltage threshold 25SYN_UV, it is regarded that the synchronism check conditions are met.

Loading...

Loading...