Titanium Interfaces User Guide

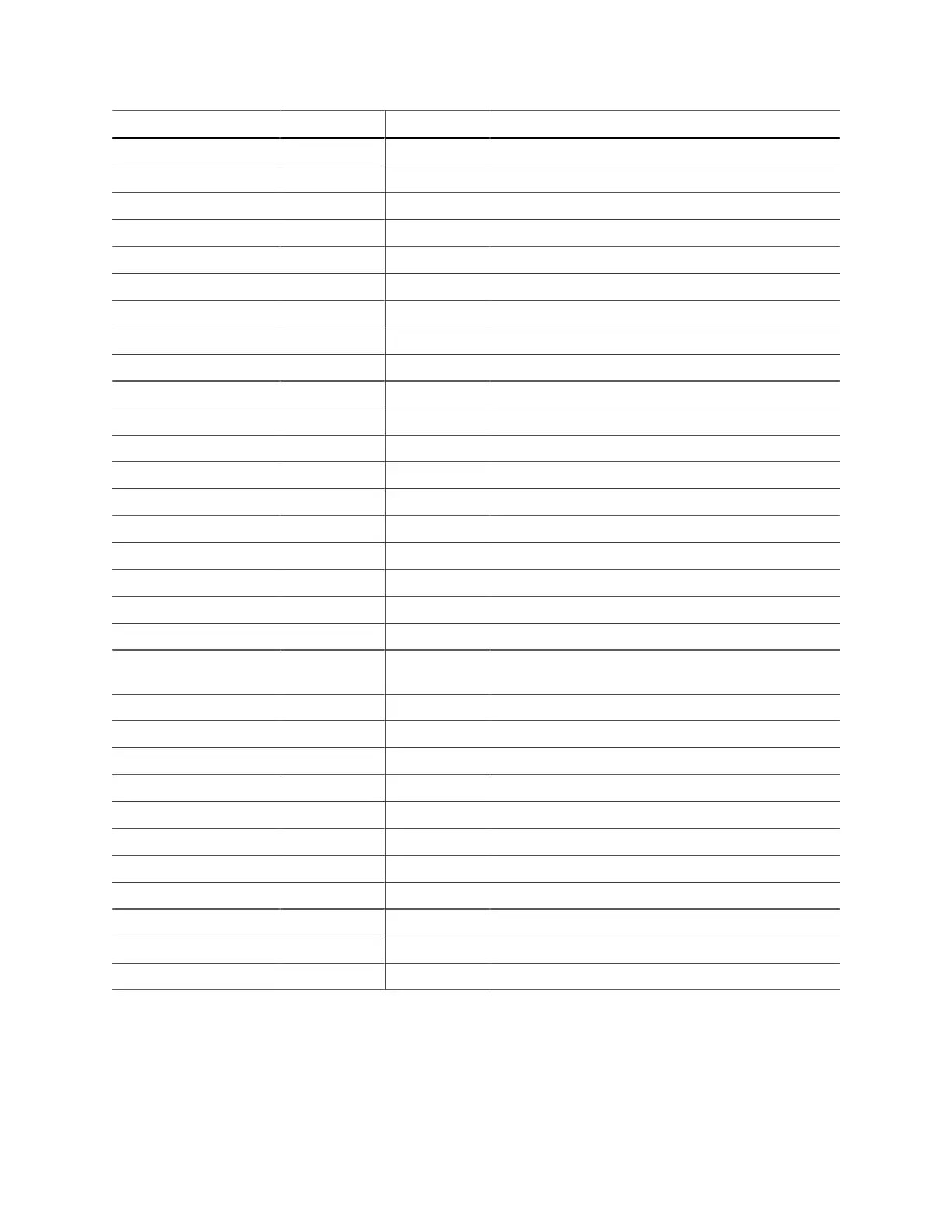

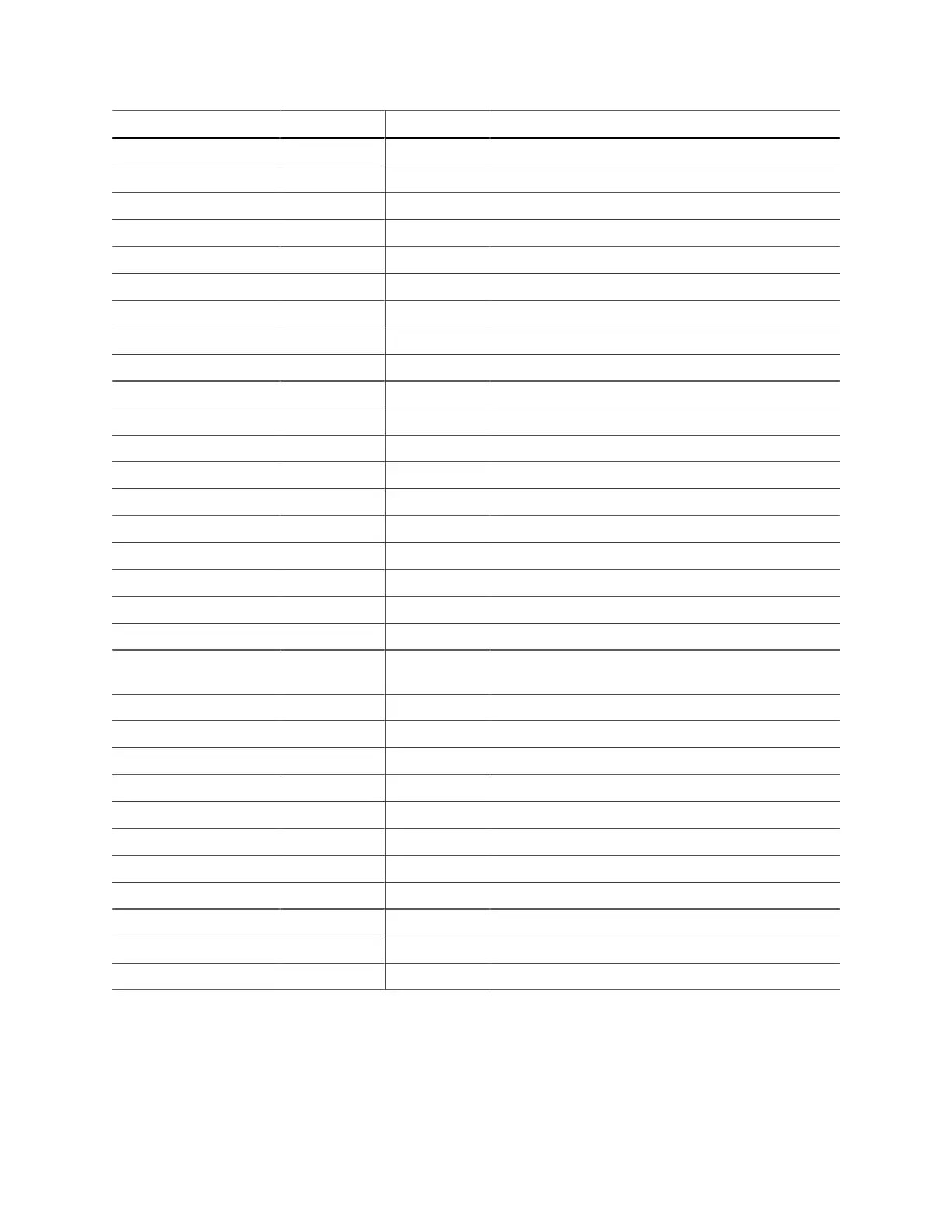

Table 11: Register Configuration Signals

Signal Direction Clock Domain Description

CR_ACLK Input N/A AXI Control Register Clock.

CR_ARESETN Input CR_CLK Register Reset (active low).

CR_ARADDR[14:0] Input CR_CLK Register Read Command Address.

CR_ARID[5:0] Input CR_CLK Register Read Command ID.

CR_ARLEN[7:0] Input CR_CLK Register Read Command Length.

CR_ARSIZE[2:0] Input CR_CLK Register Read Command Size.

CR_ARBURST[1:0] Input CR_CLK Register Read Command Burst Type.

CR_ARVALID Input CR_CLK Register Read Command Valid Indicator.

CR_ARREADY Output CR_CLK Register Is Ready to accept Read Command.

CR_AWADDR[14:0] Input CR_CLK Register Write Command Address.

CR_AWID[5:0] Input CR_CLK Register Write Command ID.

CR_AWLEN[7:0] Input CR_CLK Register Write Command Length.

CR_AWSIZE[2:0] INT CR_CLK Register Write Command Size.

CR_AWBURST[1:0] Input CR_CLK Register Write Command Burst Type.

CR_AWVALID Input CR_CLK Register Write Command Valid Indicator.

CR_AWREADY Output CR_CLK Register Is Ready to accept Write Command.

CR_BID[5:0] Output CR_CLK Register Write Response ID.

CR_BRESP[1:0] Output CR_CLK Register Write Response.

CR_BVALID Output CR_CLK Register Write Response Valid Indicator.

CR_BREADY Input CR_CLK AXI master ready to accept Write Response from

Register.

CR_RDATA[31:0] Output CR_CLK Register Read Data.

CR_RID[5:0] Output CR_CLK Register Read Data ID.

CR_RRESP[1:0] Output CR_CLK Register Read Data Response.

CR_RLAST Output CR_CLK Register Read Data Final Word Indicator.

CR_RVALID Output CR_CLK Register Read Data Valid.

CR_RREADY Input CR_CLK AXI master ready to accept Read Data from Register.

CR_WDATA[31:0] Input CR_CLK Register Write Data.

CR_WSTRB[3:0] Input CR_CLK Register Write Data Strobe.

CR_WLAST Input CR_CLK Register Write Data Final Word Indicator.

CR_WVALID Input CR_CLK Register Read Data Valid.

CR_WREADY Output CR_CLK AXI master ready to accept Read Data from Register.

www.efinixinc.com 33

Loading...

Loading...