Titanium Interfaces User Guide

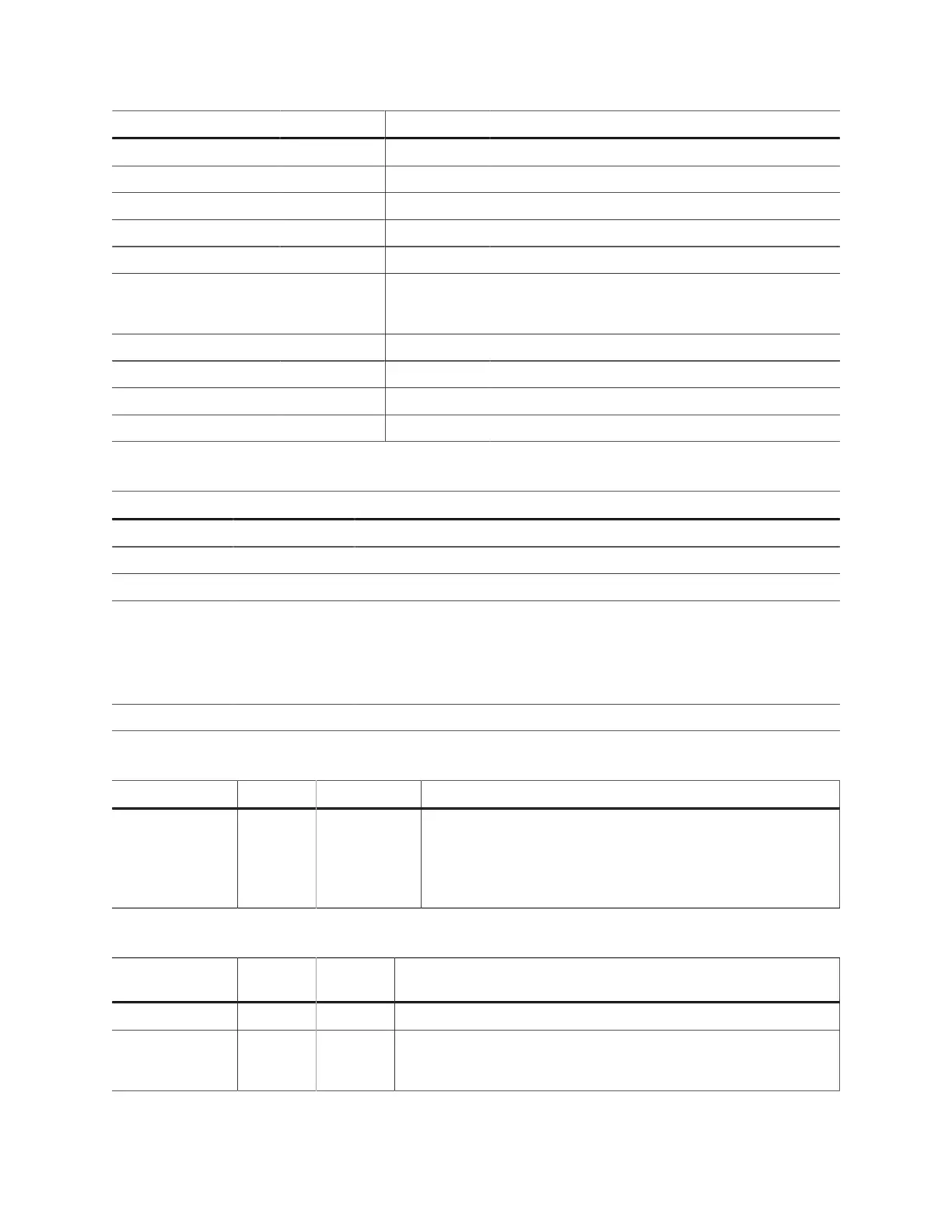

Table 12: Controller Signals

Signal Direction Clock Domain Description

CTRL_CLK Input N/A Clock to controller.

CTRL_RSTN Input CTRL_CLK Active low controller reset.

CTRL_INT Output N/A Controller detects Interrupt.

CTRL_MEM_RST_VALID Output N/A Controller has reseted.

CTRL_REFRESH Output CTRL_CLK Indicate controller is executing refresh command.

CTRL_CKE[1:0] Output CTRL_CLK Delayed 'control_cke' from the controller, indicating

that the memory is in self-refresh or power down

mode.

CTRL_BUSY Output CTRL_CLK Controller is busy reading data.

CTRL_CMD_Q_ALMOST_FULLOutput CTRL_CLK Command queue reached 'q_fullness' parameter.

CTRL_DP_IDLE Output CTRL_CLK Datapath is idle.

CTRL_PORT_BUSY[1:0] Output CTRL_CLK Indicate if port is reading data.

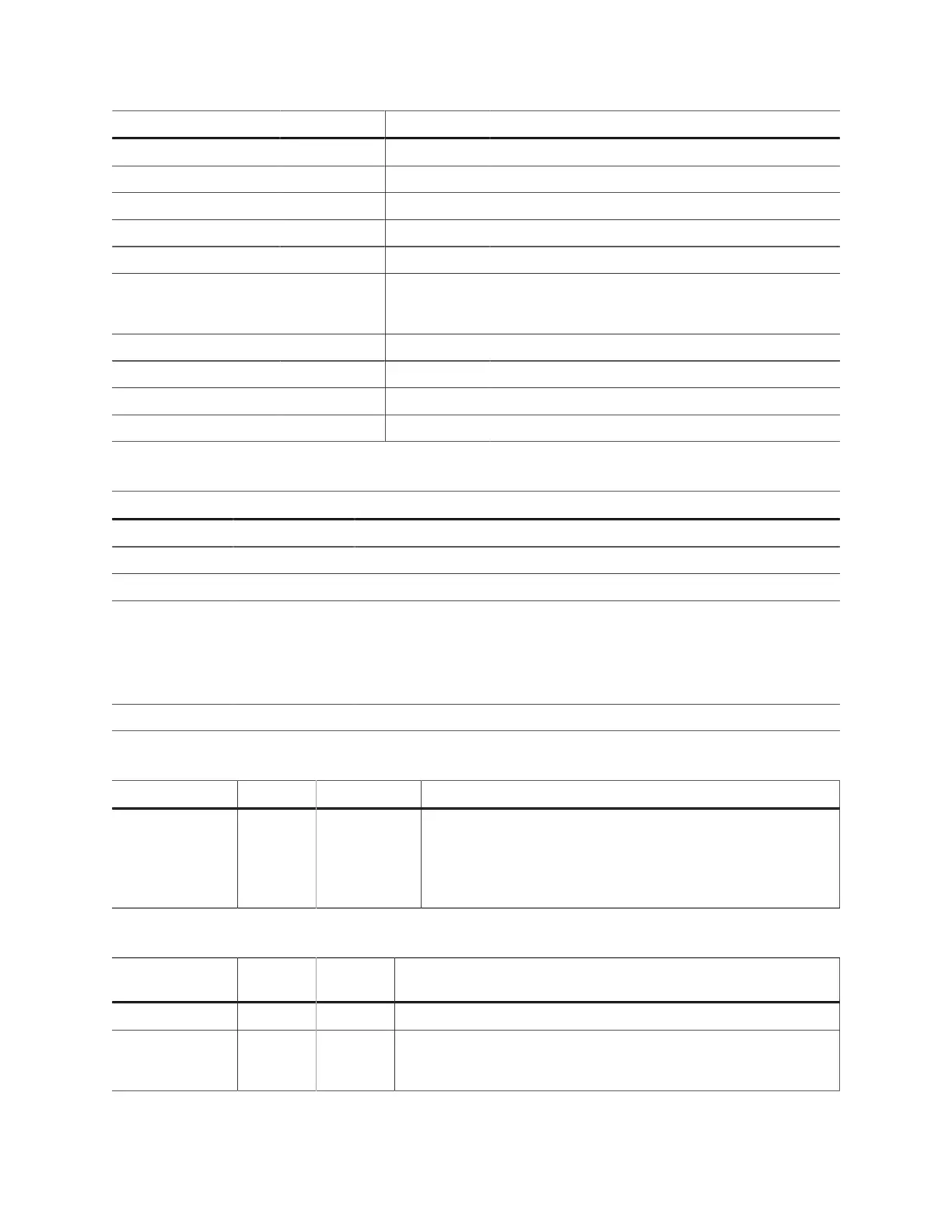

Table 13: DDR DRAM Startup Sequencer Signals

Signal Direction Description

CFG_RST Input Active-high DDR configuration controller reset.

CFG_START Input Start the DDR configuration controller.

CFG_DONE Output Indicates the controller configuration is done

CFG_SEL Input To select whether to use internal DDR configuration controller or user

register ports for configuration:

0: Use internal configuration controller.

1: Use register configuration ports (cfg_rst, cfg_start, cfg_done will be

disabled).

CFG_PHY_RSTN Input Active low reset to DDR PHY.

Table 14: PHY Signals (Interface to FPGA Fabric)

Signal Direction Clock Domain Description

CLKIN Input N/A High-speed clock to drive the DDR PHY. A PLL must generate

this clock. The clock runs at a quarter of the PHY data rate (for

example, 2000 Mbps requires a 500 MHz clock).

The DDR DRAM block uses either the PLL_TL0, PLL_TL1, or

PLL_TL2 CLKOUT4 resource as the PHY clock.

Table 15: AXI4 Gobal Signals (Interface to FPGA Fabric)

Signal Direction Clock

Domain

Description

ACLK_x Input N/A AXI4 clock inputs.

ARST_x Input ACLK_x Active-low master DDR DRAM reset. After you de-assert RST_N,

you need to reconfigure and initialize before performing memory

operations.

www.efinixinc.com 34

Loading...

Loading...