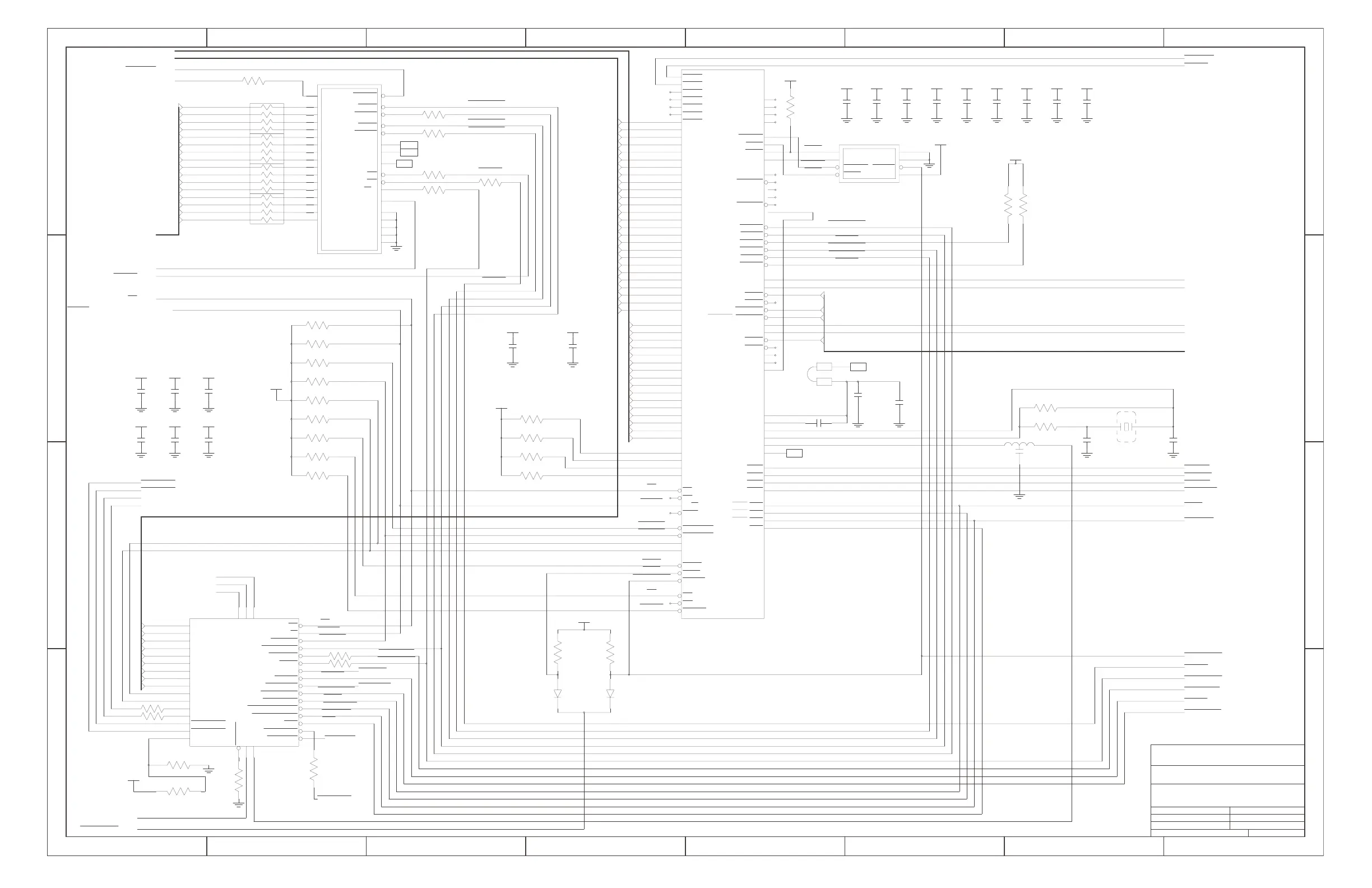

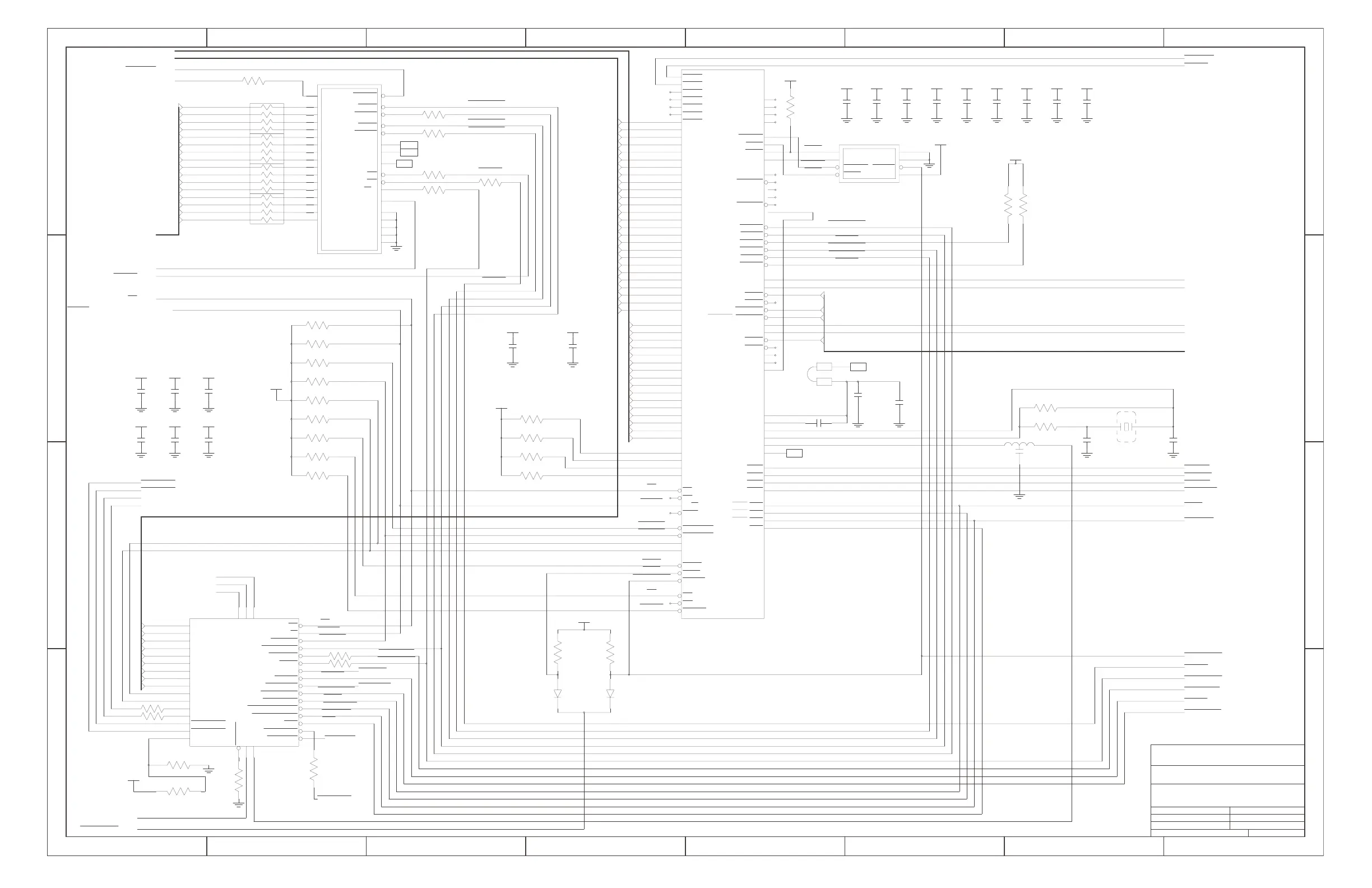

Kurzweil K2600 Series Service Manual

7-3

Chapter 7\

CPU Board–CPU, Sampler Interface (1 of 8)

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8

A

B

C

D

A

B

C

D

RP5

51

1

2

3

45

6

7

8

RP6

51

1

2

3

45

6

7

8

RP7

51

1

2

3

45

6

7

8

RP8

51

1

2

3

45

6

7

8

DGND

VCC

R/

U1

XC9536-15

K2600UC1.5

21 32 41

10 23 31

9

CA00

7

CA18

6

CA19

36

CA20

8

CA21

37

CA22

34

CA23

13

CA24

33

CA25

5

CLK

24

FLASHTYPE

40

JANISCS

25

SIZ0

1

SIZ1

11

SRAM_A18

12

SRAM_A19

17

TCK

15

TDI

30

TDO

16

TMS

29

FLASH1CS

20

FLASH2CS

42

GBLOE

3

W

27

8_BIT_CS3

14

AS

44

BYTEWR

22

CPUBUSEN

18

CPUDACK1

39

CPU_NWS_CS2

28

CS0

2

DSACK1

4

DSPCS

35

ENVRAM1

26

HIWR

19

ONE_WS_CS1

38

SCSIDACK

43

SCSIDRQ

DGND

VCC

R/

AVEC/

PB1/IRQ1/

PB2/IRQ2/

PB4/IRQ4/

PB3/

PB5/

PB6/

PB7/

OP4/FFULLA/

OP1/

OP6/

OP0/

DSCLK/

DSO/

DSI/

/A25/PA1

/A26/PA2

/A27/PA3

/A28/PA4

/A29/PA5

/A30/PA6

/A31/PA7

U3

68340

15 17 23 35 41 50 59 68 78 90 102 113 123 134 143

13 21 36 42 51 55 60 69 79 91 103 114 124 126 135 144

140

A[00]

72

A[01]

71

A[02]

70

A[03]

67

A[04]

66

A[05]

65

A[06]

64

A[07]

63

A[08]

62

A[09]

61

A[10]

58

A[11]

57

A[12]

56

A[13]

54

A[14]

53

A[15]

52

A[16]

49

A[17]

48

A[18]

47

A[19]

46

A[20]

45

A[21]

44

A[22]

43

A[23]

130

A[24]/PA0

109

D[00]

110

D[01]

111

D[02]

112

D[03]

115

D[04]

116

D[05]

117

D[06]

118

D[07]

119

D[08]

120

D[09]

121

D[10]

122

D[11]

125

D[12]

127

D[13]

128

D[14]

129

D[15]

40

FC[0]

39

FC[1]

38

FC[2]

37

FC[3]

4

SIZ[0]

3

SIZ[1]

6

AS

10

BERR

8

BG

7

BGACK

9

BR

1

DMC

5

DS

141

DSACK[0]

142

DSACK[1]

11

HALT

131

IACK1

132

IACK2

133

IACK3

136

IACK4

137

IACK5

138

IACK6

139

IACK7

12

RESET

82

TXRDYA

2

W

14

CLKOUT

18

EXTAL

27

FREEZE

22

PB0/MODCK

76

RXDA

84

RXDB

88

SCLK

31

TCK

33

TDI

34

TDO

28

TIN1

75

TIN2

32

TMS

29

TOUT1

74

TOUT2

77

TXDA

85

TXDB

19

VCCSYN

92

X1

89

X2

16

XFC

20

XTAL

26

BKPT

108

CS0

107

CS1

106

CS2

104

CS3

81

CTSA

87

CTSB

94

DACK1

97

DACK2

95

DONE1

98

DONE2

93

DREQ1

96

DREQ2

25

IFECTH

24

IPIPE

105

IRQ3

101

IRQ5

100

IRQ6

99

IRQ7

80

RTSA

86

RTSB

83

RXRDYA

30

TGATE1

73

TGATE2

J802

MOTO 8PIN BDM

7

VCC

1

VSEE1

3

VSEE2

5

RESET

2

BKPT

4

FREEZE

6

IFTECH

8

IPIPE

Y1

32.768KHZ

12

R/

J801

K25 SOB

34

+12

31

+5

33

-12

19

A1

1

G1

18

G2

24

G3

27

G4

29

G5

26

CS

20

DACK1

22

DACK2

21

DREQS

25

DRQ1

23

DRQ2

30

OE

28

W

2

D00

3

D01

4

D02

5

D03

6

D04

7

D05

8

D06

9

D07

10

D08

11

D09

12

D10

13

D11

14

D12

15

D13

16

D14

17

D15

32

RST

C9

.1uF,POLY

12

L1

1

2

L2

47pF

12

3

R15

56

12

D1

BAS70(1N270)

12

D2

BAS70(1N270)

12

R115612

R14

56

12

R33 10K

12

R36 10K

12

R35 10K

12

R34 10K

12

R19 10K

12

R27 10K

12

R26 10K

12

R25 10K

12

R24 10K

12

R23 10K

12

R22 10K

12

R21 10K

12

R20 10K

12

R32 DNS

12

R31 56

12

R30 100

12

R29 100

12

R28 100

12

R9 100

12

R18

1K

12

R37

10K

12

R41

10K

12

R40

10K

12

R39

10K

12

R38

10K

12

C2

.1uF

12

C1

.1uF

12

C119

.01uF

12

C118

.01uF

12

C117

.01uF

12

C3

.1uF

12

C8

.1uF

12

C6

.1uF

12

C13

.1uF

12

C11

.1uF

12

C20

.1uF

12

C18

.1uF

12

C19

.1uF

12

C15

.1uF

12

C17

.1uF

12

C16

.1uF

12

C10

.1uF

12

C14

.1uF

12

C12

.1uF

12

C22

20pF,NPO

12

C21

20pF,NPO

12

R8 5612

R10

56

12

R163

DNS12

R164

0.0 12

R42 20M

12

R43

330K

12

YOUNG CHANG CO., LTD.

of Young Chang Co., Ltd. is prohibited.

Reproduction without the express written consent

Filename:

Doc:

Mfg:

Eng:

Sht

By:

Date:

of

Rev:

K2600 CPU BOARD

CPU, Sampler Interface

Mike Richmond

021206-001 RDV2

021206D2 1/5/00

18

CD[15:00] {8-A1}

CA[25:00] {8-A1} SCSIEOP {4-B1}

EXTIAK {8-D1}

SCSIDRQ {4-A8}

RESET {3-B1,8-B1,D8}

VCC

VCC VCC VCC VCC VCC VCC VCC VCC VCC

SD[15] SMPDREQ2

SD[14] CPUDACK1

SD[13] CA[25]

SMPDREQ1

SD[12] CA[24]

SMPDACK1

SD[11] CA[23]

SD[10]

+12V

CA[22]

VCC

SD[09]

~12V

CA[21] BKPT

SD[08] CA[20] FREEZE

VCC

VCCSD[07] CA[19] IFETCH

SD[06] SMPCS CA[18] IPIPE

SD[05] CA[17]

SD[04] CA[16]

SD[03] CA[15]

SD[02] CA[14]

SD[01] CA[13] SCLK

SD[00] CA[12]

CA[11] SMPDREQ2

SD[15:00] {8-A8}

CA[10] CPUDACK1

CA[09] DONE1

CA[08] SMPDREQ1

CA[07] SMPDACK1

CA[06] DONE2

SA[01] {8-B8} CA[05]

SMPCS {8-A8}

CA[04]

CMIDI_RxD {8-D3}CPUOE

CA[03]

CMIDI_TxD {8-D1}

CA[02] SIZE[3]

AS {6-C1}

CA[01]

WRITE {2-B1,3-D1,5-A1,6-C1,8-A1}

CA[00] SIZE[2]

SIZE[1]

CD[15]

EXTMIDIRXD {3-C1}

VCC VCC

CD[14]

EXTMIDITXD {3-C1}

CD[13] SIZE[0]

CD[12]

SIZE[3:0] {6-B1}CD[11]

CD[10]

VCCCD[09]

VCC VCC VCC

CD[08]

VCCSYN

CD[07]

VCC

CD[06]

CD[05]

VCC

CD[04]

CD[03]

CD[02] XFCSYN

VCC VCC VCC

CLK32KRC1

CD[01] EXTAL

CD[00] XTAL

FC3

VCC

FC2

FC1

EXTIRQ {8-D3}

FC0

SCSIIRQ {4-A8}

FLASH2CS {2-D1} FDCIRQ {3-A8}

FLASH1CS {2-D1}

AS

CPUMUTE {5-D1}

SRAM_A18 {2-D1}

SRAM_A19 {2-D1}

WRITE

8_BIT {8-A1}

ONE_WS {8-A1}

DSACK0

DSACK1

SIZ1

SIZ0

BERR

HALT

TDO_DEV1 {6-C1} RESET_68K

TMS {5-A8,6-C1}

TDI_DEV1 {5-A8} BR

BGACK

VCC

CA[25] AS

CA[24] WRITE

CA[23] DSACK1

CA[22] CPUDACK1

CA[21] CPUWE_HI

RESET_68K {8-D1}

CA[20] CPUWE_LO

CPUOE {2-D1,3-B1,4-B1,6-C1}CA[19]

JANISCS {8-A1}

CA[18] DSPCS

CPUWE_LO {2-D1}

CA[00]

ENVRAM1 {2-D1}

CPUWE_HI {2-D1,3-B1,4-B1}SIZ1 CPUBUSEN

SIZ0 8_BIT

DSPCS {8-A1}

CPU_NWS

CPUBUSEN {8-A1}ONE_WS

CS0

SCSIDRQ {4-A8}

VCC

SCSIDACK {4-B1}

TCLK {5-A8,6-B1} CCLKOUT

PWRUPRST {8-C8}

These Bypass caps are for U1.

JTAG DEV1

Sht. 1 of 8

Eng:

Date:

Doc:

Loading...

Loading...