Display

NVIDIA Jetson Nano DG-09502-001_v2.1 | 39

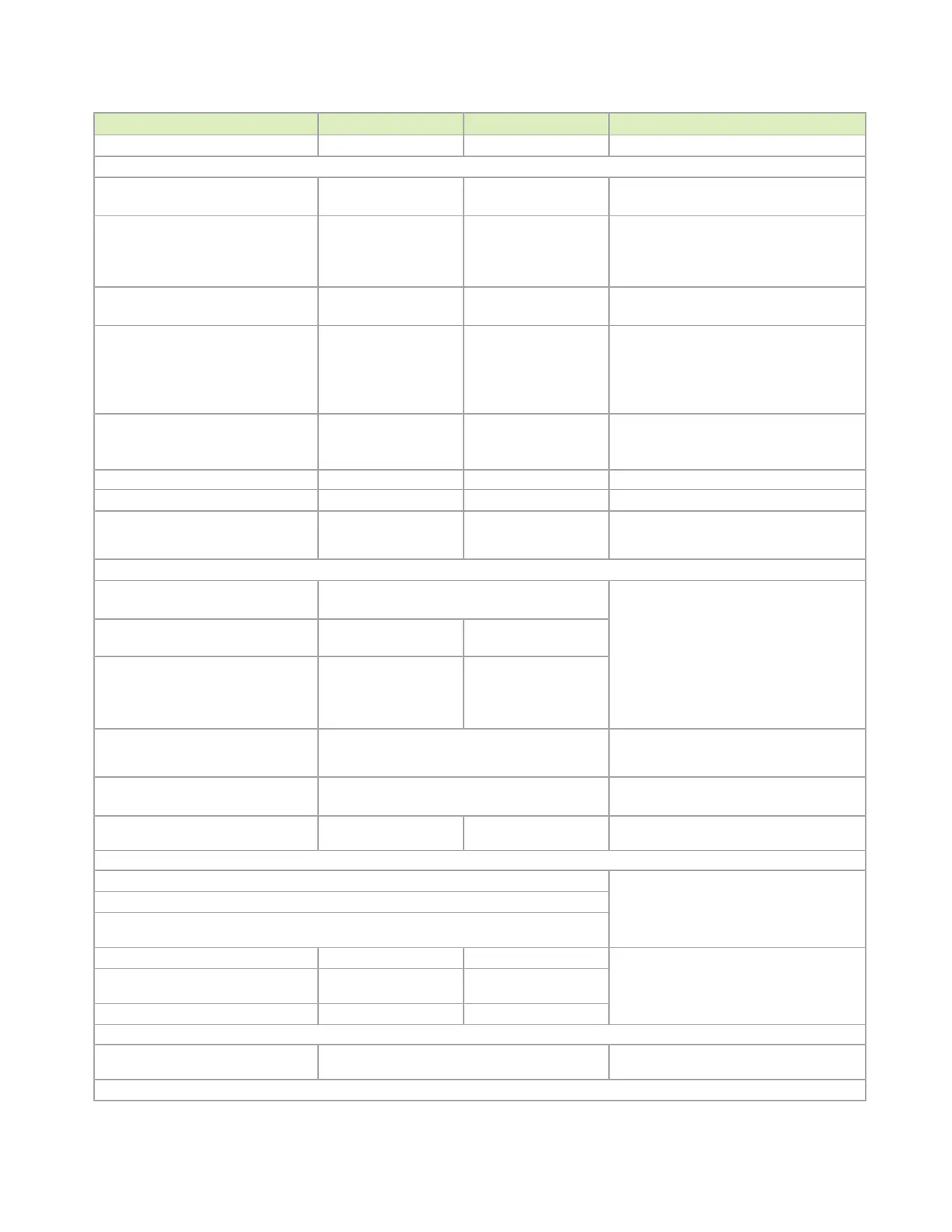

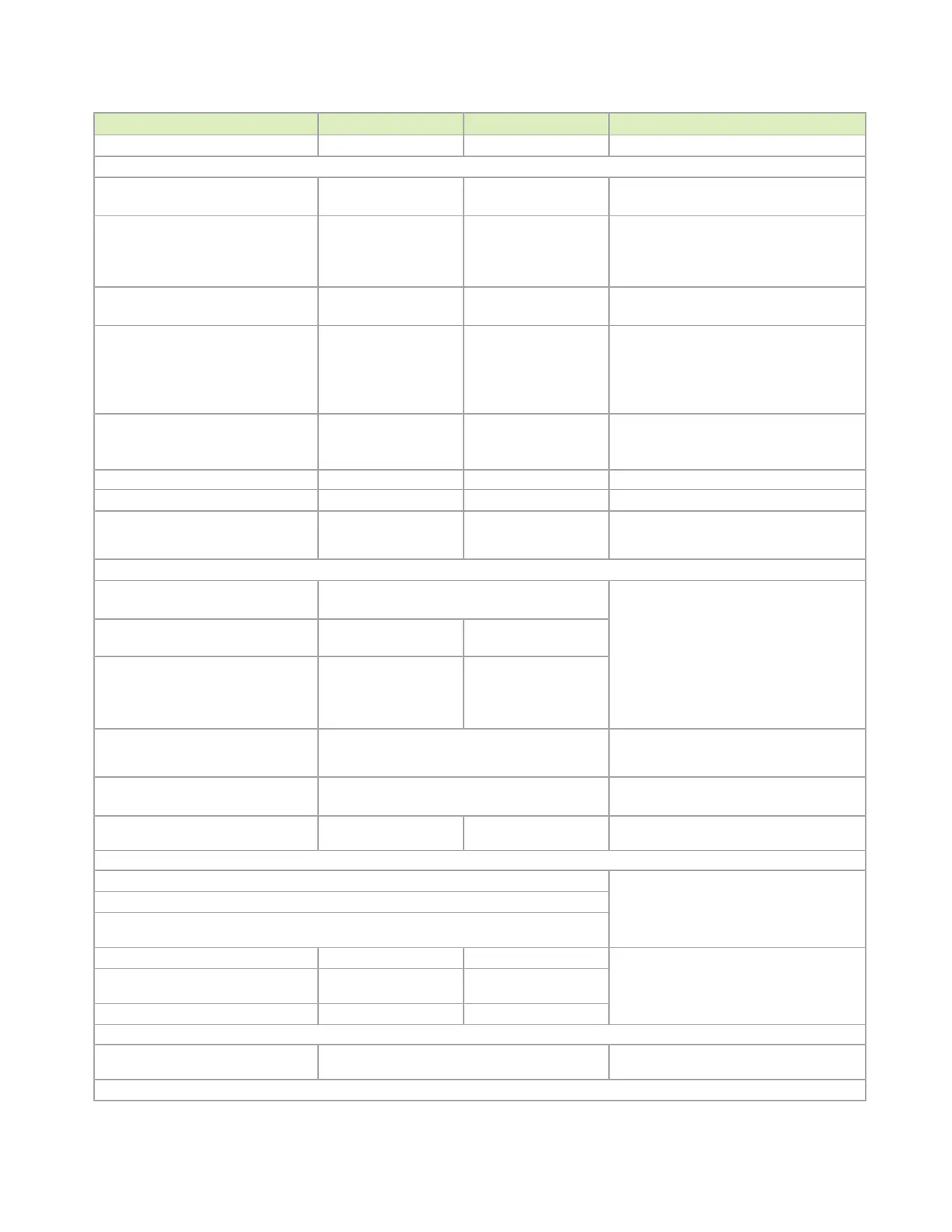

Parameter Requirement Units Notes

Reference plane GND

Trace spacing/Length/Skew

Trace loss characteristic: < 0.8

< 0.4

dB/in. @ 3GHz

dB/in. @ 1.5GHz

The max length is derived based on this

characteristic. See Note 1.

Trace spacing (pair-pair)

Stripline

Microstrip: pre 1.4b

Microstrip: 1.4b/2.0

3x

4x

5x to 7x

dielectric

For Stripline, this is 3x of the thinner of above and

below.

Trace spacing Stripline

(Main link to DDC) Microstrip

3x

5x

dielectric For Stripline, this is 3x of the thinner of above and

below.

Max total length/delay (1.4b/2.0 - up to

5.94Gbps)

Stripline

Microstrip (5x spacing)

Microstrip (7x spacing)

63.5/2.5 (437)

50.8/2.0 (300)

63.5/2.5 (375)

mm/in (ps)

Propagation delay: 175ps/in. for stripline, 150ps/in.

for microstrip).

Max Total Length/Delay (Pre-1.4b)

(up to 165Mhz) Microstrip

Stripline

254/10 (1 500)

225/8.5 (1500)

mm/in (ps) Propagation delay: 175ps/in. for stripline, 150ps/in.

for microstrip).

Max intra-pair (within pair) skew 0.15 (1) mm (ps) See notes 1, 2, and 3

Max inter-pair (pair to pair) skew 150 ps See notes 1, 2, and 3

Max GND transition via distance 1x Diff pair via pitch

For signals switching reference layers, add one or

two ground stitching vias. It is recommended they

be symmetrical to signal vias.

Via

Topology Y-pattern is recommended

keep symmetry

Xtalk suppression is the best by Y-p a t te r n. Al so , it

can reduce the limit of pair-pair distance. Need

review (NEXT/FEXT check) if via placement is not Y-

pattern. See Figure 7-11

Minimum impedance dip 97

92

Ω@200ps

Ω@35ps

Recommended via dimension

drill/pad

Antipad

via pitch

200/400

840

880

uM

GND via

Place GND via as symmetrically as possible to data pair

vias. Up to four signal vias (2 diff pairs) can share a single

GND return via

GND via is used to maintain return path, while its

Xtalk suppression is limited

Max # of vias PTH via

u-via

4 if all vias are PTH via

Not limited if total channel loss meets IL spec.

Max via stub length 0.4 mm long via stub requires review (IL and resonance dip

check)

Topology

The main route via dimensions should comply with the via structure rules (See via section) See Figure 7-8

For the connector pin vias, follow the rules for the connector pin vias (See via section)

The traces after main route via should be routed as 100Ω dif ferential or as uncoupled 50ohm SE traces on

PCB top or bottom.

Max distance from RPD to main trace (seg B) 1 mm

Max distance from AC cap to RPD stubbing

point (seg A)

~0 mm

Max distance between ESD and signal via 3 mm

Add-on Components

Example of a case where space is limited for

placing components.

Top: See Figure 7-12 Bottom: See Figure 7-13

AC Cap

Loading...

Loading...