138

Operating Modes Section 5-2

• HR area, Timer/Counter PVs, DM area, and AR area data will be

cleared when the power is turned OFF.

• SR area data will become unstable when the power is turned OFF.

Therefore, do not set the I/O Hold Bit (SR 25212) and the Forced Sta-

tus Hold Bit (SR 25211) to be maintained in the PC Setup (DM 6601).

• The I/O Hold Bit (SR 25212), the Forced Status Hold Bit (SR 25211), and

the Output OFF Bit (SR 25215) will be particularly unstable and may have

an adverse effect on operation. Turn OFF these bits at the start of the pro-

gram. The following instructions can be used to do this.

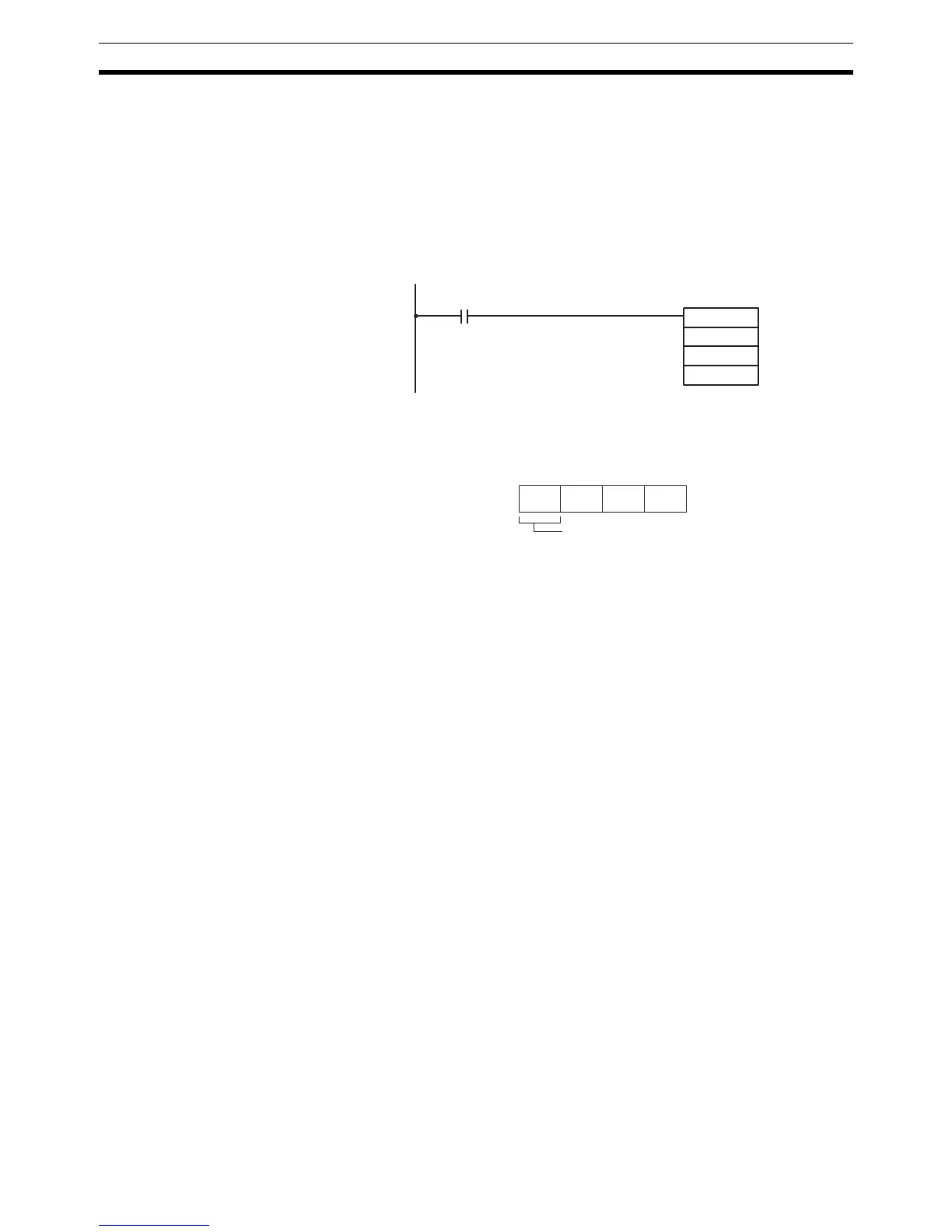

If the setting shown below is made in the PC Setup (DM 6655 bits 12 to 15),

battery errors (a non-fatal error) will not be detected even if the internal bat-

tery expires.

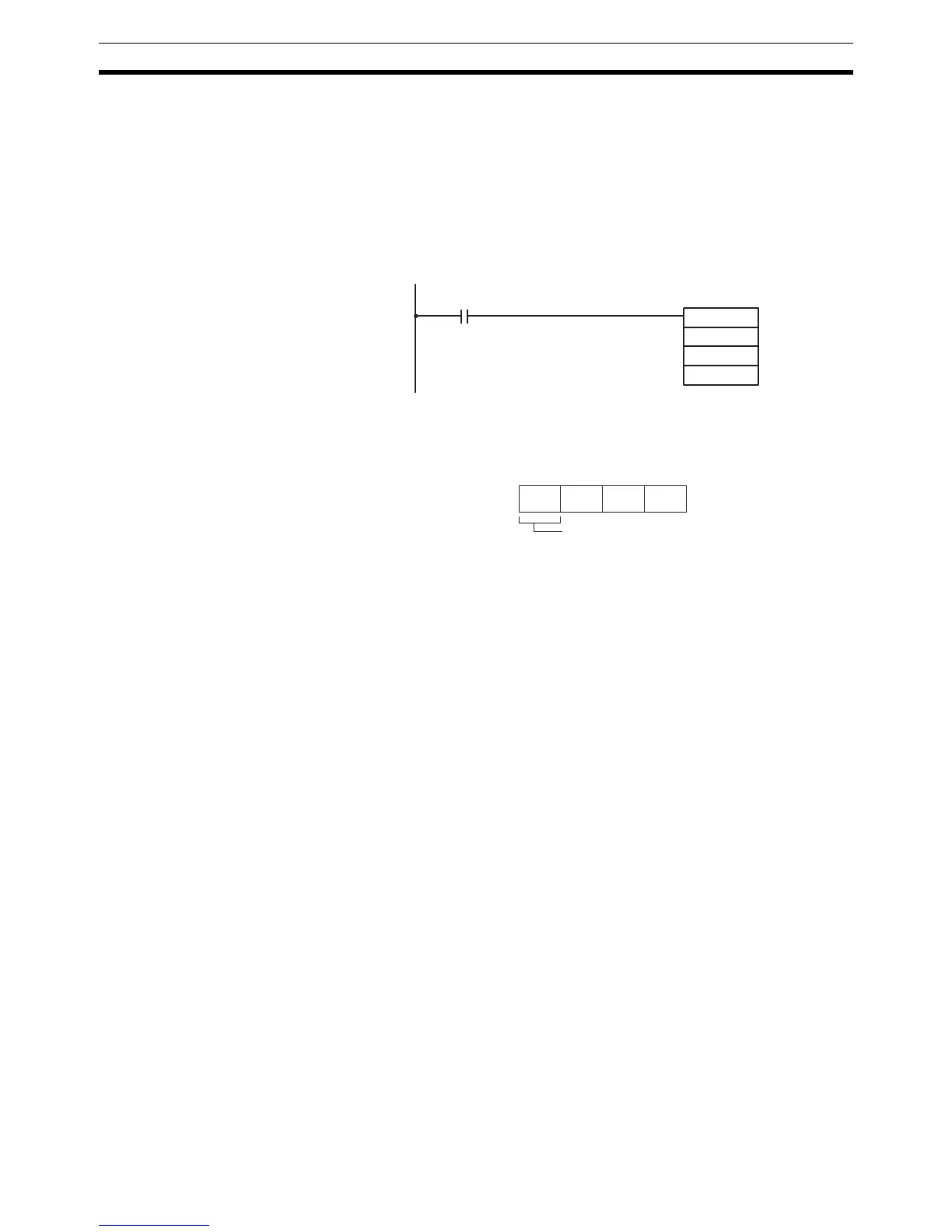

First Cycle Flag

(Turns ON for 1

cycle at the start of

operation.)

25315

ANDW(34)

#67FF

252

252

DM 6655

15 12

Low Battery Error Enable

0 Hex: Detected

1 Hex: Not detected

11 08 07 04 03 00

Loading...

Loading...