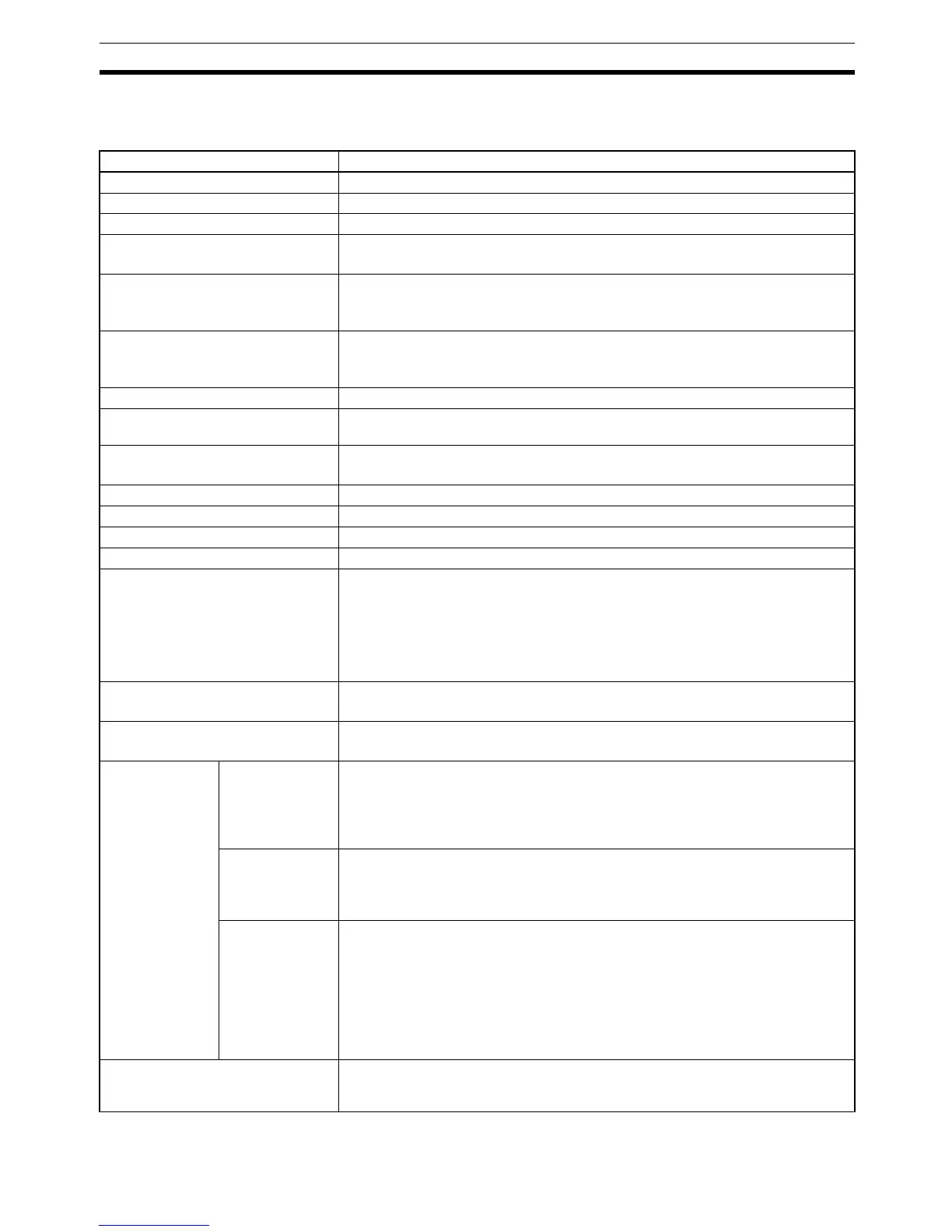

45

Unit Specifications Section 2-1

2-1-2 CPU Unit Specifications

Performance Specifications

Item Specifications

Control method Stored program method

I/O control method Cyclic scan and direct output/immediate interrupt processing used together

Programming language Ladder diagram

I/O capacity

CQM1H-CPU11/21: 256

CQM1H-CPU51/61: 512

Program capacity

CQM1H-CPU11/21: 3.2 Kwords

CQM1H-CPU51: 7.2 Kwords

CQM1H-CPU61: 15.2 Kwords

Data memory capacity

CQM1H-CPU11/21: 3 Kwords

CQM1H-CPU51: 6 Kwords

CQM1H-CPU61: 12 Kwords (DM: 6 Kwords; EM: 6 Kwords)

Instruction length 1 to 4 words per instruction

Number of instructions in instruction

set

162 (14 basic, 148 special instructions)

Instruction execution times

Basic instructions: 0.375 to 1.125 µs

Special instructions: 17.7 µs (MOV instruction)

Overseeing time 0.70 ms

Mounting structure No Backplane (Units are joined horizontally using connectors)

Mounting DIN Track mounting (screw mounting not possible)

CPU Unit built-in DC input points 16

Maximum number of Units Maximum number of I/O and Dedication I/O Units (Analog Power Supply Units

must also be counted.)

CPU Block only: 11 Units max.

CPU Block and Expansion I/O Block

CPU Block: 5 Units max.

Expansion I/O Block: 11 Units max.

Inner Boards

CQM1H-CPU11/21: None

CQM1H-CPU51/61: 2 Boards

Communications Units

CQM1H-CPU11/21: None

CQM1H-CPU51/61: 1 Unit

Types of

interrupts

Input interrupts

(4 points max.)

Input Interrupt Mode: Interrupt is executed in response to input from an external

source to the CPU Unit’s built-in input points.

Counter Mode: Interrupt is executed in response to input received a certain

number of times (counted down) via the CPU Unit’s internal built-in input points

(4 points).

Interval timer

interrupts

(3 points max.)

Scheduled Interrupt Mode: Program is interrupted at regular intervals measured by

one the CPU Unit’s internal timers.

One-shot Interrupt Mode: One interrupt is executed after a certain time, measured

by one of the CPU Unit’s internal timers.

High-speed

counter interrupt

Target Value Comparison: Interrupt is executed when the high-speed counter PV

is equal to a specified value.

Range Comparison: Interrupt is executed when the high-speed counter PV lies

within a specified range.

Note Counting is possible for high-speed counter inputs from the CPU Unit’s inter-

nal input points, Pulse I/O Boards, or Absolute Encoder

Interface Boards. (The High-speed Counter Board has no interrupt function,

and can only output bit patterns internally and externally.)

I/O allocation I/O is automatically allocated in order from the Unit nearest to the CPU Unit.

(Because there are no I/O tables, it is not necessary, and not possible, to create

I/O tables from a Programming Device.)

Loading...

Loading...