G.2

SEL-749M Relay Instruction Manual Date Code 20080918

Relay Word Bits

Definitions

Definitions

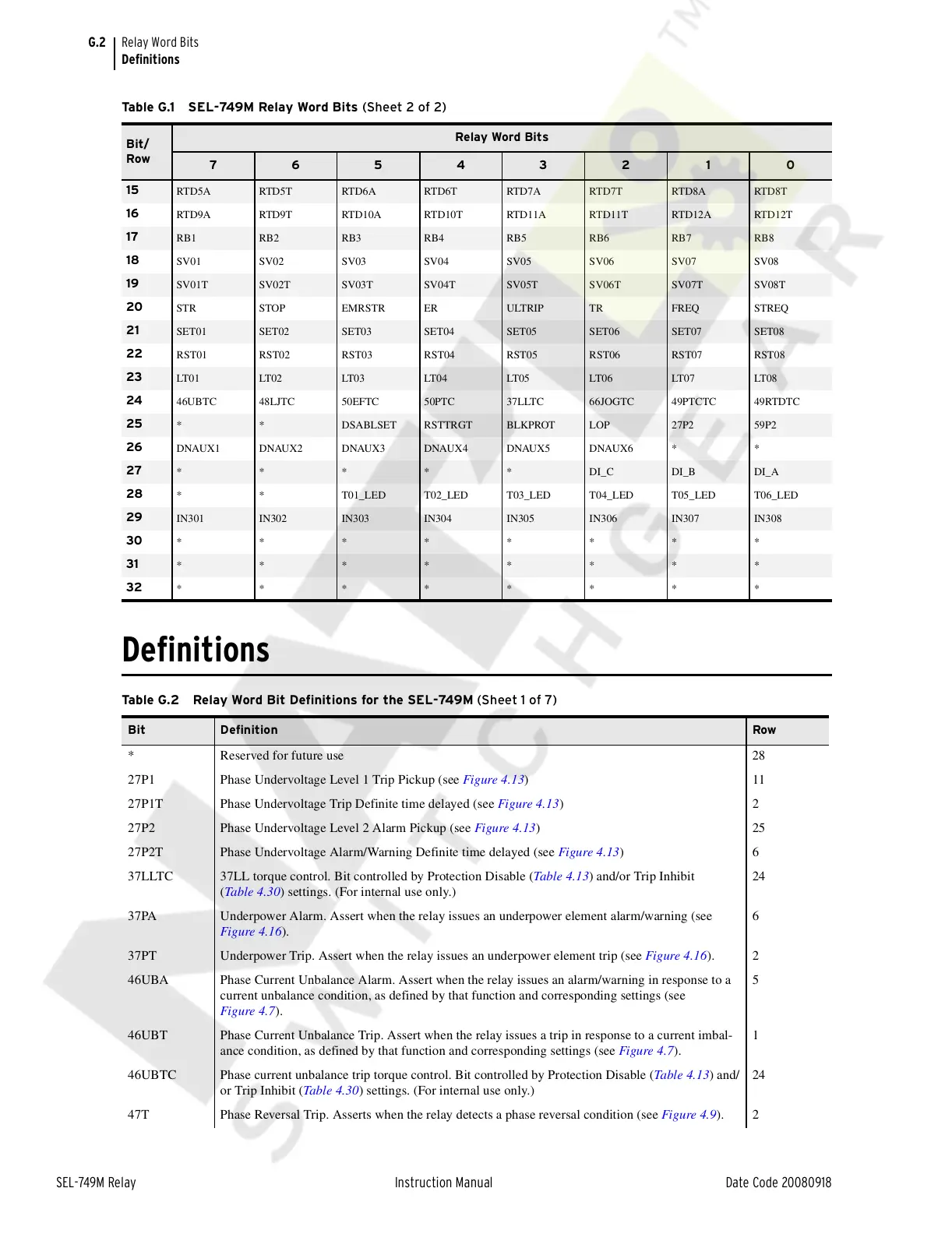

15

RTD5A RTD5T RTD6A RTD6T RTD7A RTD7T RTD8A RTD8T

16

RTD9A RTD9T RTD10A RTD10T RTD11A RTD11T RTD12A RTD12T

17

RB1 RB2 RB3 RB4 RB5 RB6 RB7 RB8

18

SV01 SV02 SV03 SV04 SV05 SV06 SV07 SV08

19

SV01T SV02T SV03T SV04T SV05T SV06T SV07T SV08T

20

STR STOP EMRSTR ER ULTRIP TR FREQ STREQ

21

SET01 SET02 SET03 SET04 SET05 SET06 SET07 SET08

22

RST01 RST02 RST03 RST04 RST05 RST06 RST07 RST08

23

LT0 1 LT02 LT0 3 LT0 4 LT 05 LT06 LT 07 LT08

24

46UBTC 48LJTC 50EFTC 50PTC 37LLTC 66JOGTC 49PTCTC 49RTDTC

25

* * DSABLSET RSTTRGT BLKPROT LOP 27P2 59P2

26

DNAUX1 DNAUX2 DNAUX3 DNAUX4 DNAUX5 DNAUX6 * *

27

* * * * * DI_C DI_B DI_A

28

* * T01_LED T02_LED T03_LED T04_LED T05_LED T06_LED

29

IN301 IN302 IN303 IN304 IN305 IN306 IN307 IN308

30

********

31

* * * * * * * *

32

********

Ta b l e G .1 S EL - 749 M Re l a y Wo r d B i ts (Sheet 2 of 2)

Bit/

Row

Relay Word Bits

7 6 5 4 3 2 1 0

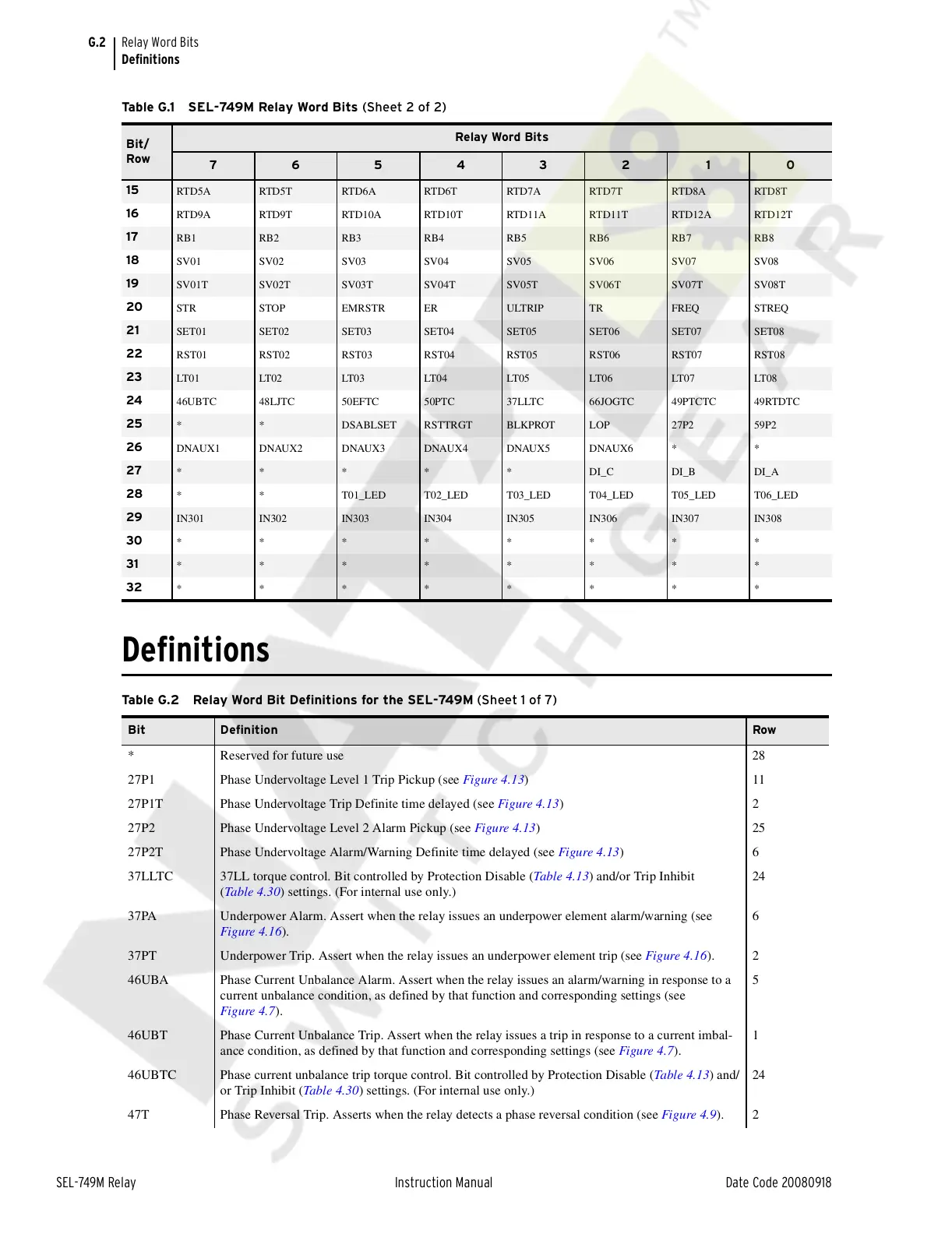

Table G.2 Relay Word Bit Definitions for the SEL-749M (Sheet 1 of 7)

Bit Definition Row

* Reserved for future use 28

27P1 Phase Undervoltage Level 1 Trip Pickup (see Figure 4.13)11

27P1T Phase Undervoltage Trip Definite time delayed (see Figure 4.13)2

27P2 Phase Undervoltage Level 2 Alarm Pickup (see Figure 4.13)25

27P2T Phase Undervoltage Alarm/Warning Definite time delayed (see Figure 4.13)6

37LLTC 37LL torque control. Bit controlled by Protection Disable (Table 4.13) and/or Trip Inhibit

(Table 4.30) settings. (For internal use only.)

24

37PA Underpower Alarm. Assert when the relay issues an underpower element alarm/warning (see

Figure 4.16).

6

37PT Underpower Trip. Assert when the relay issues an underpower element trip (see Figure 4.16). 2

46UBA Phase Current Unbalance Alarm. Assert when the relay issues an alarm/warning in response to a

current unbalance condition, as defined by that function and corresponding settings (see

Figure 4.7).

5

46UBT Phase Current Unbalance Trip. Assert when the relay issues a trip in response to a current imbal-

ance condition, as defined by that function and corresponding settings (see Figure 4.7).

1

46UBTC Phase current unbalance trip torque control. Bit controlled by Protection Disable (Table 4.13) and/

or Trip Inhibit (Table 4.30) settings. (For internal use only.)

24

47T Phase Reversal Trip. Asserts when the relay detects a phase reversal condition (see Figure 4.9). 2

Courtesy of NationalSwitchgear.com

Loading...

Loading...