PVA-3000 Reference Manual

December 2, 2019 Sifos Technologies

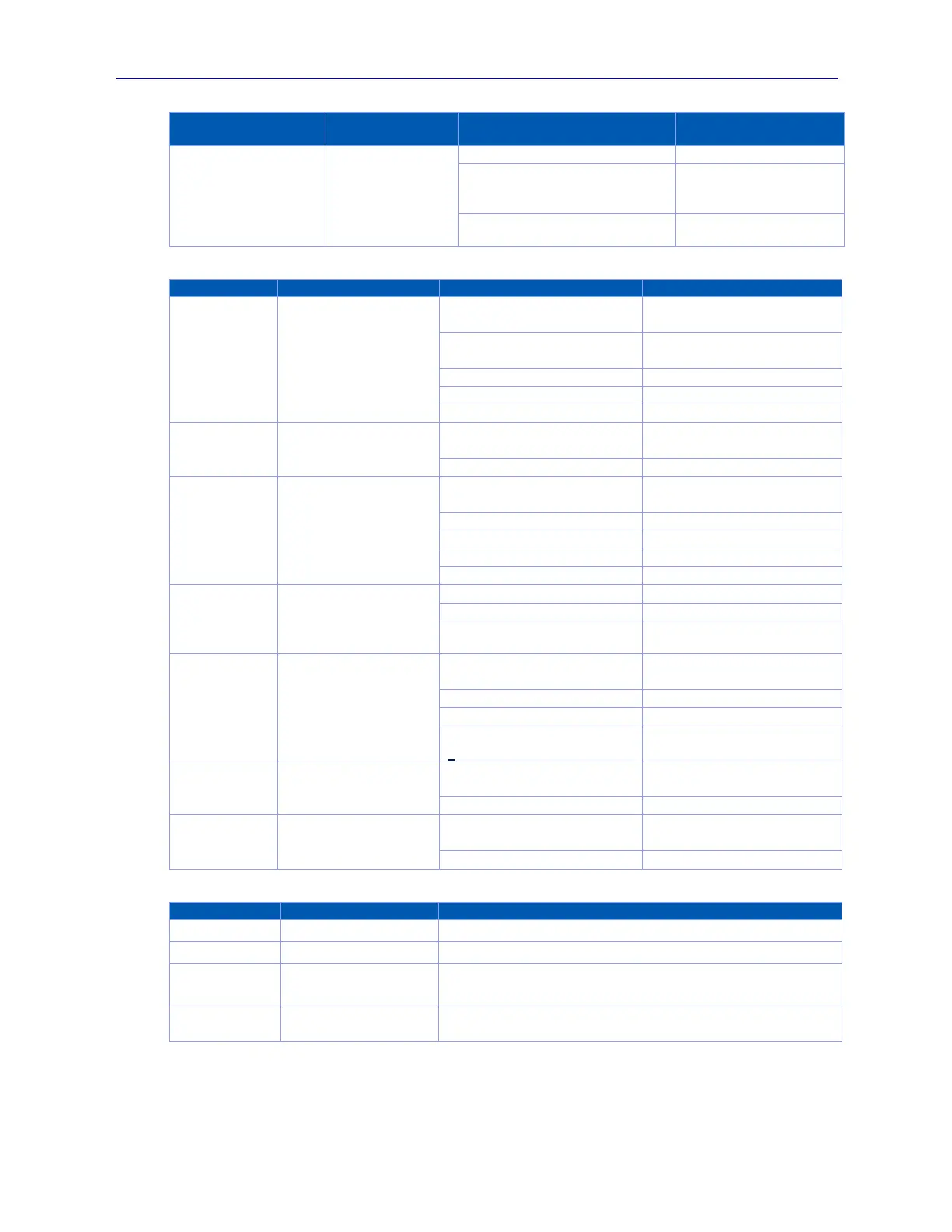

Link Partner Capabilities

& Linkup Timing

Auto-Negotiation Capabilities

Auto-Negotiation Responses

MDI/MDI-X,

MASTER/SLAVE, etc.

(see Section 5.2)

Auto-Negotiation and Linkup

Timing Analysis

20msec timing resolution

from physical connection

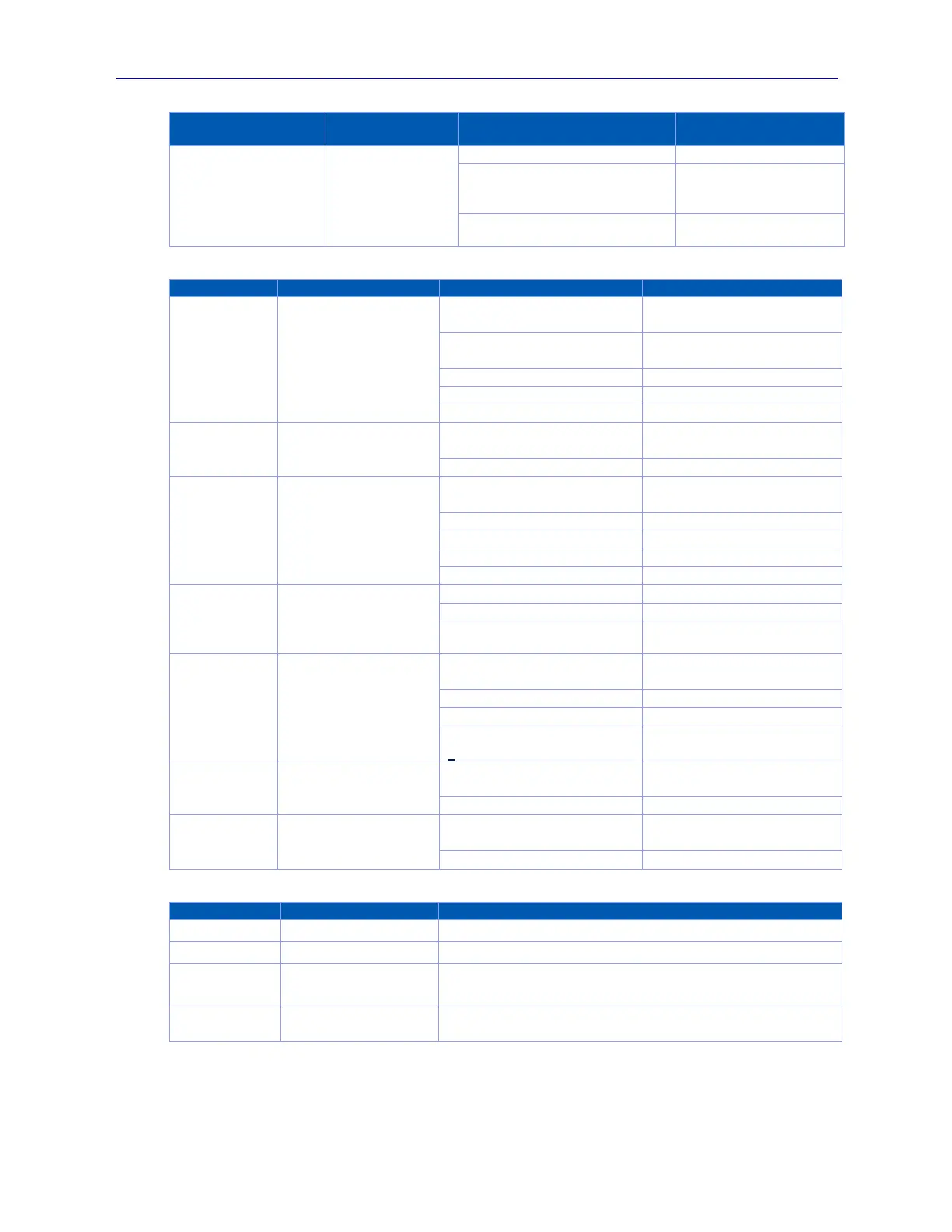

2.7.5. Impairment Synthesis Specifications

IEEE 802.3

Line Loss

Emulation

Frequency Response Target

(5 MHz – 62.5 MHz)

-(2.1 * F

0.529

+ 0.4/F) dB

± 0.5 dB (F in MHz)

Frequency Response Target

(62.5 MHz – 100 MHz)

-(2.1 * F

0.529

+ 0.4/F) dB

± 1.5 dB (F in MHz)

Return Loss (1 – 100 MHz)

Phase Linearity (4 – 100 MHz)

± 12

o

from Linear (typical)

TEST Port connected to

Test PHY or THRU Port

Fixed Return Loss

(TEST Port, 1 – 100MHz)

Pairs 1+3, 2+4, or 1+2+3+4

TEST Port connected to

Test PHY or THRU Port

Amplitude Range

relative to 40mVpp (= 0dB)

Amplitude Steps (Resolution)

Pairs 1+3, 2+4, or 1+2+3+4

Transmit

Frequency

Offset

Test Port with

Test PHY Connected

Nominal Transmit Frequency

Nominal Transmit Duty Cycle

-115, -100, -50, 0, +50, +100,

+115 ppm

Transmit

Frequency Jitter

Test Port with

Test PHY Connected

Jitter Magnitude Range

relative to 1.4 nsec pk-pk (=0dB)

Jitter Level Steps (Resolution)

Jitter Power @ greater than

+ 5 KHz w.r.t. Total Jitter Power

-13.5 dB ± 1 dB (sharp filter)

-8 dB ± 0.6 dB (1

st

order filter)

Test Port with

Test PHY Connected

Mid-Range Output Power

10/100/1000BaseT Peak Ampl.

-2.7dB (IEEE Spec.)

at Tx Level = ~6 out of 10

-4 dB to -1.9 dB (IEEE Spec)

Test Port with

Test PHY Connected

~0.2V/nsec

at setting = 5 out of 8

~0.1V/nsec to ~0.27 V/nsec

2.7.6. LED Indicators

ON: 1000BaseT, BLINKING: 100BaseT, OFF: 10BaseT

ON: Link Up, OFF: Link Down

Line Impairment

Connection

ON: 100M Cat5e Line Impairment Connected

OFF: Line Impairment Removed

ON or BLINKING: Indicates Host Communications to PVA-3102

Test Port

2.7.7.

Loading...

Loading...