Forward Error Correction in IP Networks 181

ID: um_t2gateway CP560 DVB-T2 Gateway User’s Manual Rev. 2.2 (3686)

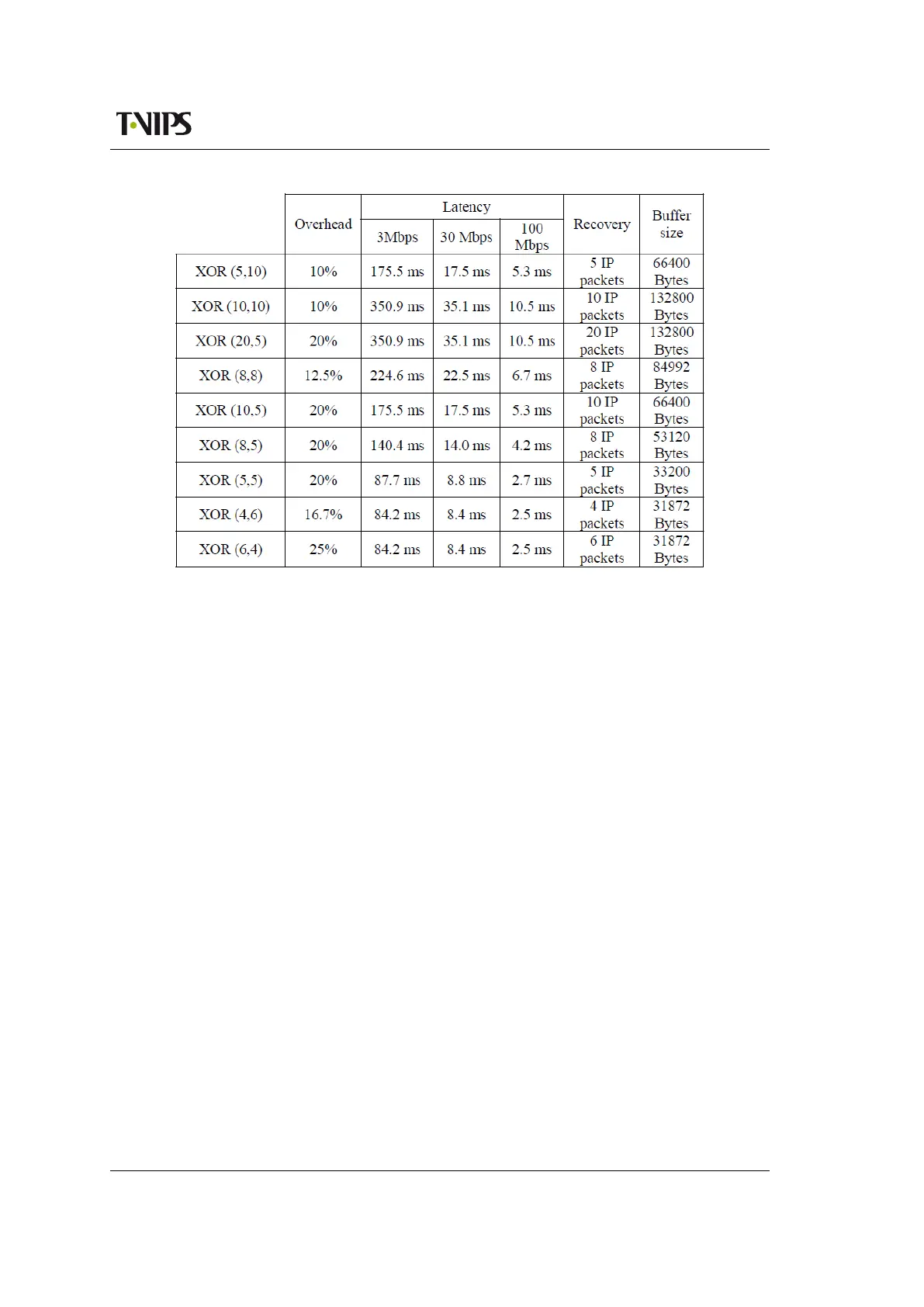

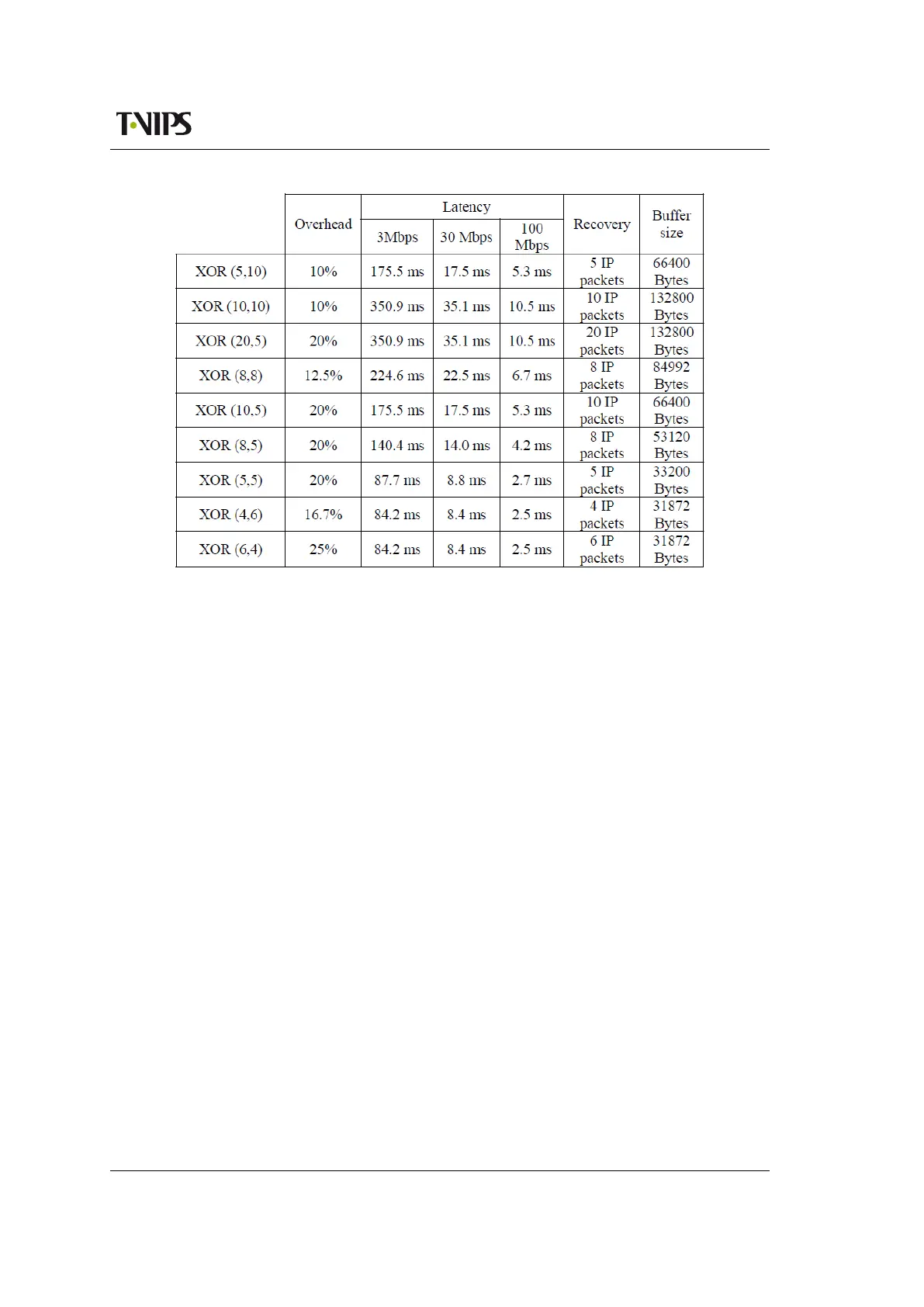

Figure C.11 FEC latency and buffer size

Also shown is the resulting overhead and the number of packets that can be corrected. In

column-only FEC there is one FEC packet per column, resulting in a 1/D increase in transmission

overhead, D being the matrix column depth. I.e. in a 10 row matrix (D=10) the added overhead

is 10%. The minimum allowable column depth of 4 will produce 25% overhead.

In two-dimensional FEC there will be D+L FEC packets in a DxL matrix (L being the row

length). Thus the added overhead is D+L/DxL, which for a 10 by 10 matrix amounts to 20%.

Adding row-FEC will increase the error correcting capability without significantly increasing the

latency or buffer size requirement. Applying row- and column-FEC also enables use of iterative

FEC calculations to recover more missing packets. The equipment manufacturer is at liberty to

determine the algorithm used in error recovery as long as the requirements and limitations of

the specification are respected.

Loading...

Loading...