Virtex-4 FPGA Configuration User Guide www.xilinx.com 47

UG071 (v1.12) June 2, 2017

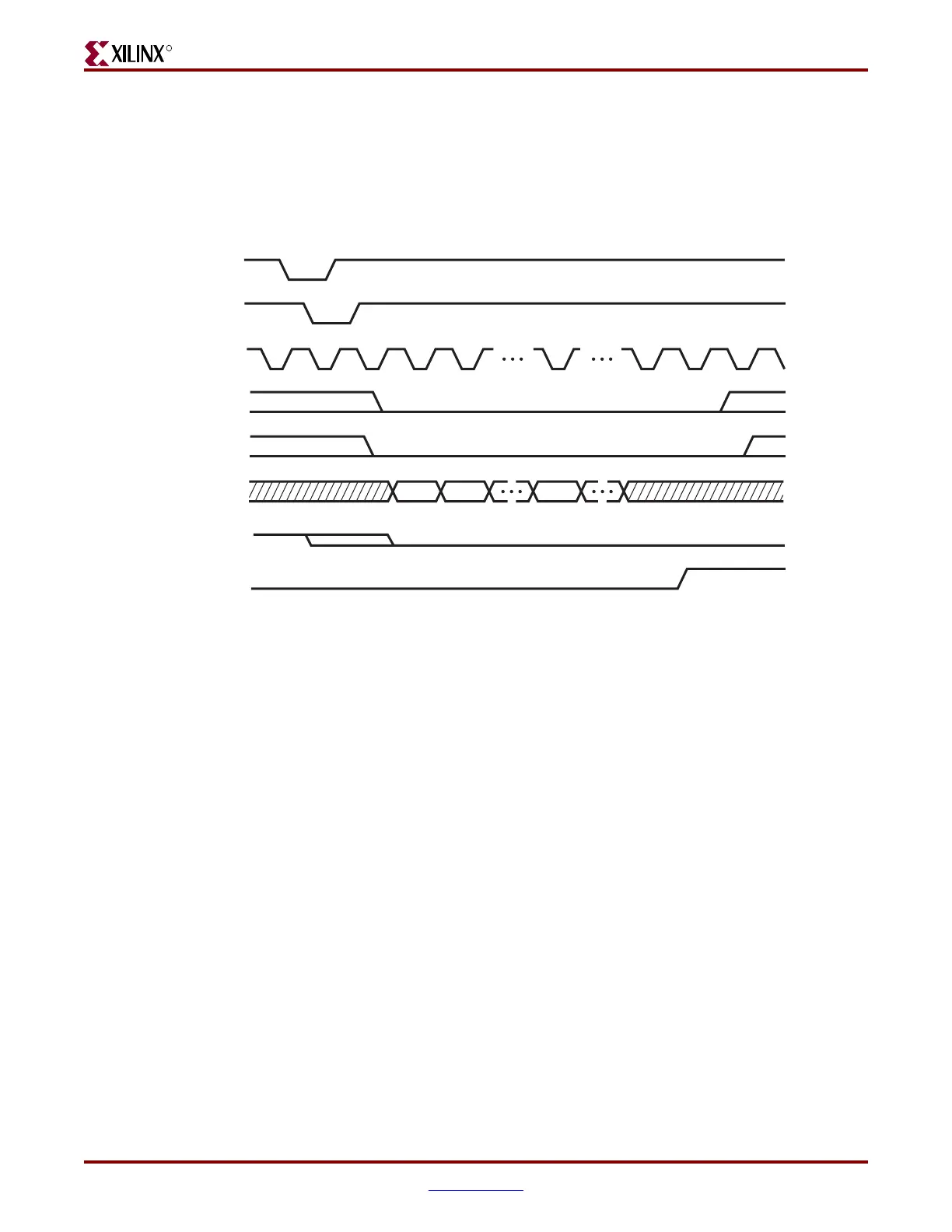

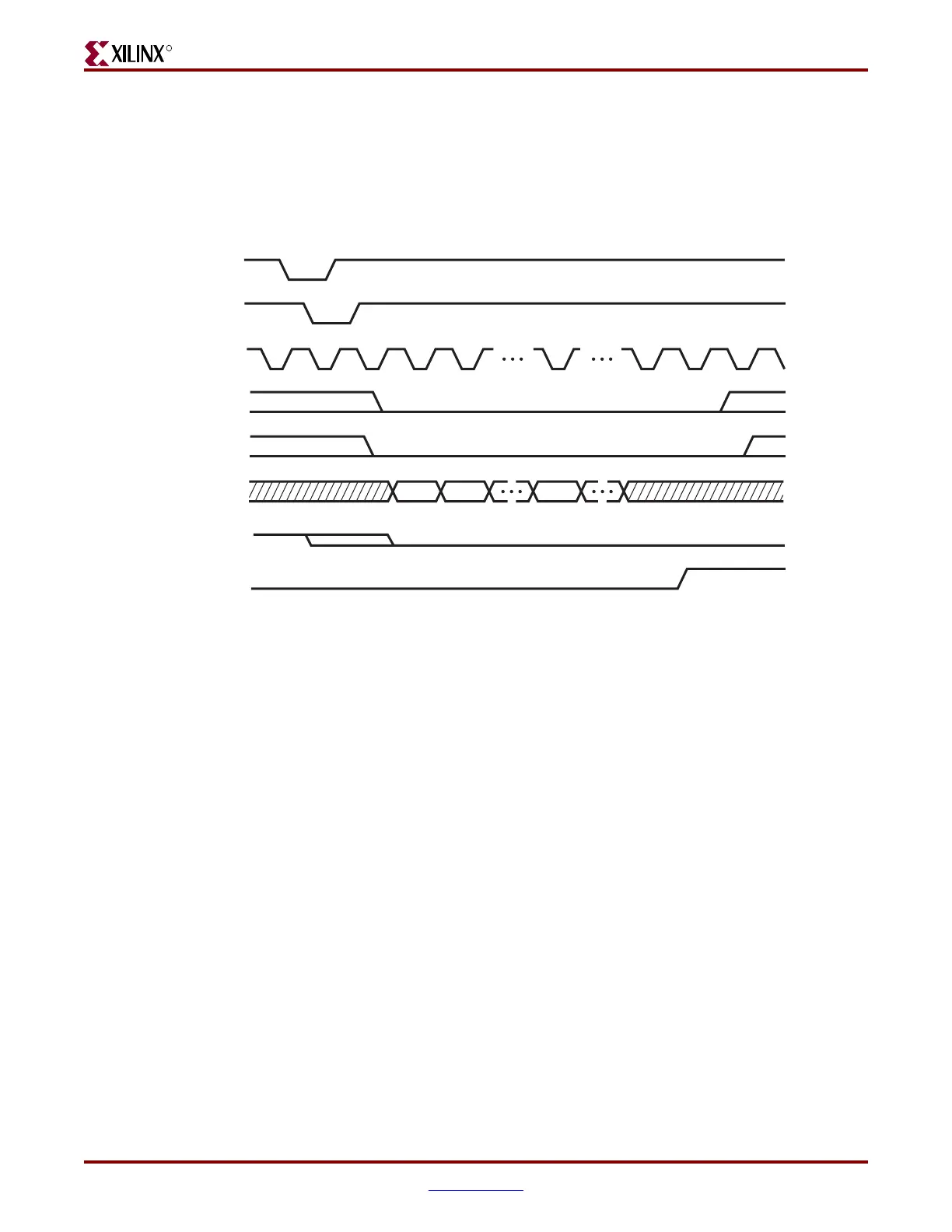

SelectMAP Configuration Interface

finished. (This can require several CCLK pulses after DONE goes High. See “Startup (Step

8)” in Chapter 1 for details).

After configuration, the CS_B and RDWR_B signals can be deasserted, or they can remain

asserted. Because the SelectMAP port is inactive, toggling RDWR_B at this time does not

cause an abort. Figure 2-16 summarizes the timing of SelectMAP configuration with

continuous data loading.

Notes relevant to Figure 2-16:

1. CS_B signal can be tied Low if there is only one device on the SelectMAP bus. If CS_B

is not tied Low, it can be asserted at any time.

2. RDWR_B can be tied Low if readback is not needed. RDWR_B should not be toggled

after CS_B has been asserted, because this triggers an ABORT. (See “SelectMAP

ABORT”).

3. If CS_B is tied Low, BUSY is tristated and pulled up until INIT_B toggles High.

4. The MODE pins are sampled when INIT_B goes High.

5. RDWR_B should be asserted before CS_B to avoid causing an abort.

6. CS_B is asserted, enabling the SelectMAP interface.

7. BUSY remains in high-Z state until CS_B is asserted.

8. With 8-bit SelectMAP, the first byte is loaded on the first rising CCLK edge after CS_B

is asserted.

9. The configuration bitstream is loaded one byte per rising CCLK edge.

10. After the last byte is loaded, the device enters the startup sequence.

11. The startup sequence lasts a minimum of eight CCLK cycles. See “Startup (Step 8)” in

Chapter 1

12. The DONE pin goes High during the startup sequence. Additional CCLKs can be

required to complete the startup sequence. (See “Startup (Step 8)” in Chapter 1).

13. After configuration has finished, the CS_B signal can be deasserted.

14. After the CS_B signal is deasserted, RDWR_B can be deasserted.

Figure 2-16: Continuous SelectMAP Data Loading

PROGRAM_B

INIT_B

CCLK

CS_B

RDWR_B

DATA[0:7]

ug071_25_073007

Byte 0 Byte 1 Byte n

BUSY

DONE

(1)

(2)

(3)

(4)

(5)

(7)

(6)

(8) (9) (10) (11)

(12)

(13)

(14)

High-Z

Loading...

Loading...