UG-1828 Preliminary Technical Data

Rev. PrB | Page 114 of 277

RECEIVER/OBSERVATION RECEIVER SIGNAL CHAIN

The ADRV9001 offers dual receive channels. With a minimum number of external components, each receive channel could build a

complete RF-to-bits signal chain which serves as RF front end for a wide range of applications. It supports both time division duplexing

(TDD) and frequency division duplexing (FDD) modes and reception of both narrowband (NB) and wideband (WB) signals up to 40

MHz. NB applications include DMR, P25 and TETRA, while WB applications are geared towards LTE transmissions. For example,

ADRV9001 supports standard sample rates of 24 kHz (typically for FM waveforms), 144 kHz and 288 kHz (typically for TETRA signals),

and 1.92 MHz, 3.84 MHz, 7.68 MHz, 15.36 MHz, 23.04 MHz, 30.72 MHz, and 61.44 MHz (typically for LTE signals). Besides those

standard rates, the ADRV9001 is also capable of supporting an almost continuous range of sample rates between 24 kHz and 61.44 MHz.

Some sample rates could not be supported due to internal clocking constraints.

Rx2

HP ADC

AFE

RX1A+

RX1A–

RX1B+

RX1B–

Rx1

DFE

DIGITAL SIGNAL PROCESSING:

– NARROW/ WIDE BAND DECIMATION

– DC OFFSET CORRECTION (DC)

– QUADRATURE ERROR CORRECTION (QEC)

– NUMERICALLY CONTROLLED OSCILLATOR (NCO)

– PROGRAMMABLE FIR FILTER (pFIR)

– RECEIVER SIGNAL STRENGTH INDICATOR (RSSI)

– FREQUENCY OFFSET CORRECTION

– PHASE OFFSET CORRECTION

– OVERLOAD DETECTORS

DATA PORT

CMOS-SSI

OR

LVDS-SSI

TO

BBP

LP ADC

LP ADC

HP ADC

INTERNAL

OBSERVATION

LPF

LO1

LO2

LPF

90°

0°

24159-095

Figure 122. Top Level Structure of ADRV9001 Dual Receiver

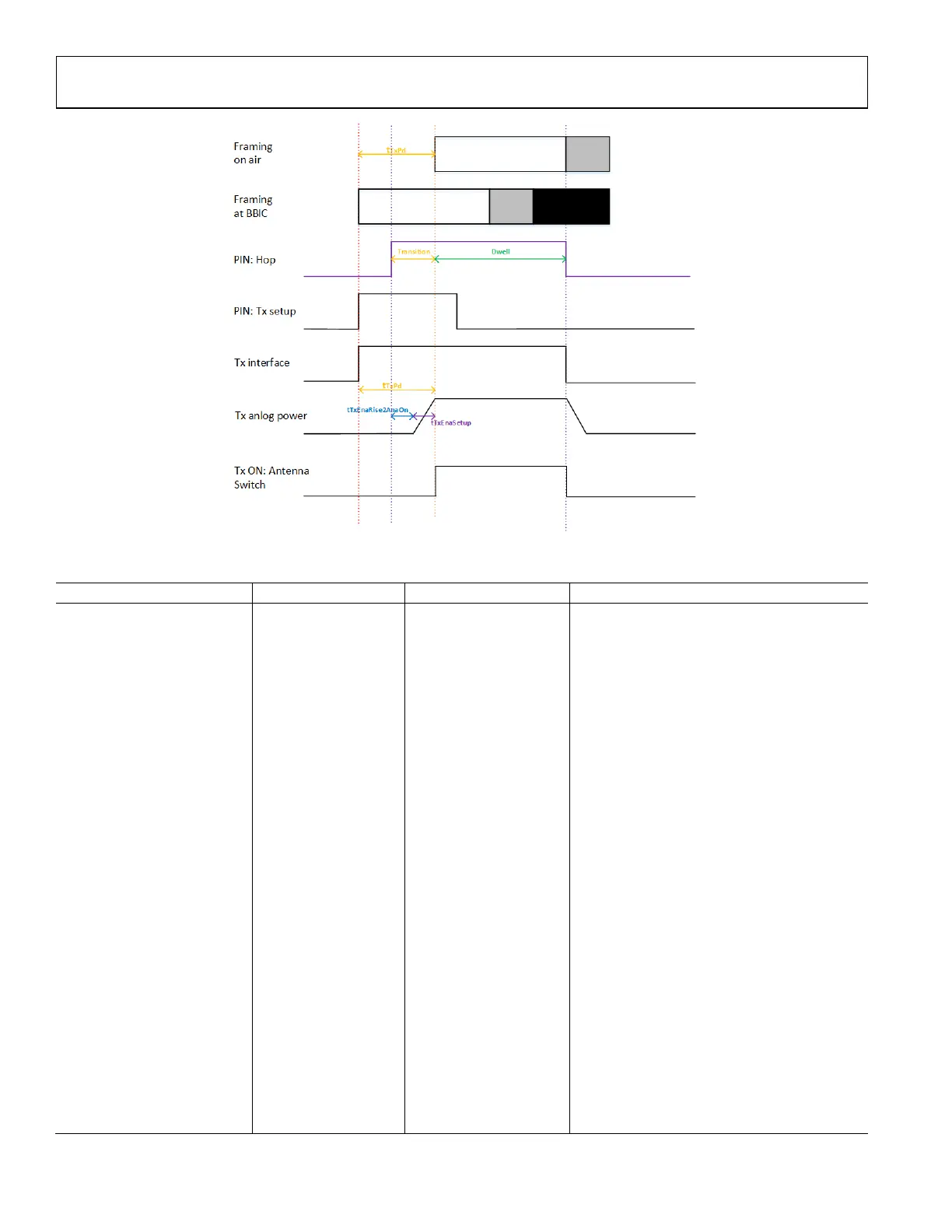

Figure 122 describes the top-level structure of the ADRV9001 receivers. As shown in Figure 122, each receive path Rx1 or Rx2 contains 2

major subsystems, the Analog Front End (AFE) and the Digital Front End (DFE). The AFE subsystem contains 4 major components,

which are programmable front end attenuator, matched I and Q mixer, low pass filter (LPF) and analog-to-digital converter (ADC). The

attenuators are used to control the signal gain to avoid overloading the datapath when a strong interfering signal presents. It is followed

by the mixers to down convert the received signals for digitization. The output current of the mixers is further converted to voltage and

filtered by LPFs before passing to ADCs. The ADRV9001 provides two pairs of ADCs, a pair of high performance (HP) ADCs to achieve

high linearity performance and a pair of low power (LP) ADCs with slightly less linearity performance but significant lower power

consumption. This design allows for a flexible trade-off between power consumption and linearity performance.

The DFE subsystem contains a series of digital signal processing components such as sample rate decimation (DEC), dc offset correction (DC),

quadrature error correction (QEC), digital down conversion (DDC) with numerically controlled oscillator (NCO), a programmable 128-tap

FIR filter (PFIR), receiver signal strength indicator (RSSI), frequency offset correction (FOC), phase offset correction (POC) and

overload detectors. DEC is used to decimate the ADC sample rate to the desired output sample rate. DC, QEC, PFIR, FOC and POC are

used to condition the digital signals at different stages of the datapath for optimal performance. Overload detectors are used for gain

control in the datapath. RSSI provides signal power measurement to control the bit-width of the output signal. In addition, it could be

used to detect the presence of a signal in a desired frequency band. At the end of the signal chain, through CMOS-SSI or LVDS-SSI data

port, the output signal is delivered to based band processor for further processing.

The ADRV9001 supports a RF local oscillator (LO) range from 30 MHz to 6 GHz. RF LOs can be generated via two internal phase lock

loops (PLL) or applied externally to the part. The digital subsystem contains an optional digital mixer that is driven by a programmable

NCO. Receiver LO can offset from the frequency of the desired channel and then make use of the digital mixer to down convert the

signal to baseband before being processed by baseband processor. There are several advantages to offset the receiver LO from the

frequency of the desired channel: Impairments that exist around the receiver LO, such as LO-leakage, can be avoided. The effect of flicker

noise from baseband circuits can be mitigated since the received signal is offset from dc in the analog signal path. Also, image rejection

can be improved if the receiver LO is offset enough from the desired channel, such that the image frequency lies in the attenuation region

of the user’s external RF filter. IF operation could work with both NB and WB applications. Typically, when the receiver is operating in

NB mode, the sensitivity requirements for these applications demand very low noise performance, therefore, the intermediate frequency

(IF) approach is preferred. The device is capable of receiving signals offset from the carrier, as well as an IF down conversion scheme.

When the receiver is operating on a WB signal, it could use direct down conversion or zero IF (ZIF) (although IF approach is also

available for WB signal). In this mode the DDC will be bypassed.

Loading...

Loading...