Preliminary Technical Data UG-1828

Rev. PrB | Page 119 of 277

LP

ADC

LP

ADC

16 BITS

LPF OUTPUT

LPF OUTPUT

LPADC

HPADC

2p2G

1p47G

1p1G

16 BITS

HP

ADC

HP

ADC

ADC_H

ADC_L

ADC CLK

MUX

WB RX MUX

ADC_M

2211.84M

1105.92M

1474.56M

5 BITS

5 BITS

DEC/8

DEC/12

DEC/6

DEC/3 DEC/8

DEC/16

DEC/32

DEC/2

DEC/4

184.32MHz

61.44MHz

30.72MHz

46.08MHz

DEC/2

23.04MHz

46.08MHz

DEC/40 DEC/40

DEC/24

DEC/8

DEC/6

DEC/4

1152kHz

15.36MHz

7.68MHz

3.84MHz

192kHz

144kHz

48kHz

288kHz

24kHz

1.92MHz

61.44MHz

LTE20M

LTE40M_1

LTE15M

LTE10M

LTE5M

LTE3M

LTE1.4M

LTE40M_2

NB RX MUX

DMR48K

TETRA_1

TETRA_192K

DMR_R0

DMR_R1

P25_1_R1

FM_R1

TETRA_2

DEC/4

24159-098

Figure 125. Decimation Schemes in Receiver Data Chain to Support Various Standards

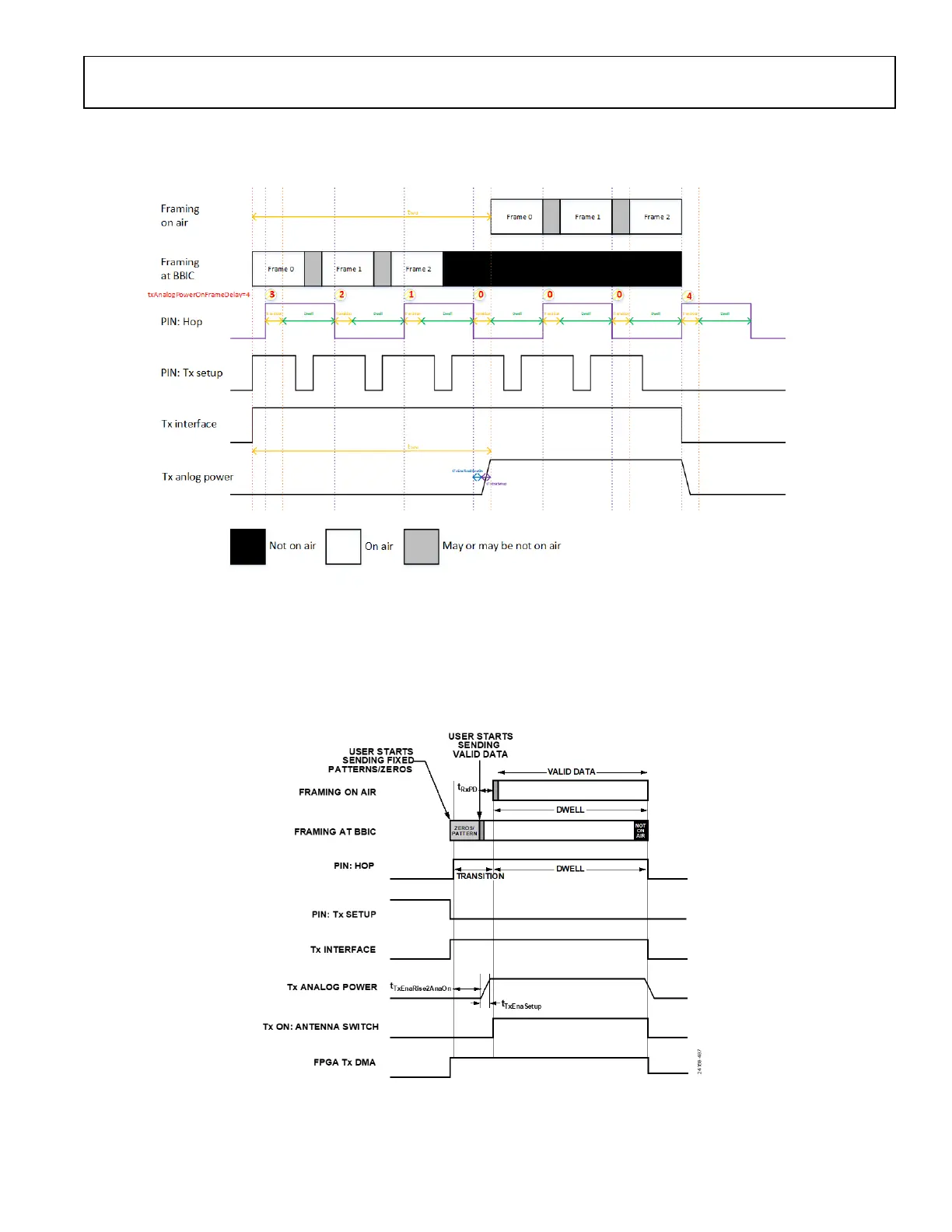

As shown in Figure 125, in NB and WB mode, 3 different ADC output sample rates are first decimated to a fix rate of 184.32 MHz. Then,

it is further converted to 2 different rates, one is 61.44 for WB mode only and the other is 46.08 MHz for both NB and WB modes. All

LTE standard modes are considered WB and the desired sample rate is further generated from both 61.44 MHz and 46.08 MHz through

a decimation rate of 2 to 32. DMR, FM, P25 and Tetra are NB modes and the desired sample rate is further generated from 46.08 MHz

with a decimation rate of 160-1920.

For each decimator show in Figure 125, it could consist a combination of lower rate decimation filters. For example, DEC/40 could be

implemented as a cascade of DEC/10 and 2 DEC/2 decimators. In addition, the different decimation rates are achieved by strategically

enabling and disabling some lower rate decimators. For example, in WB mode, with an initial sample rate of 61.44 MHz, if all lower rate

decimators are used, it can achieve a decimation rate of 32. If two of the DEC/2 are disabled, a decimation rate of 8 can be achieved. All

the decimation filters are carefully designed to satisfy the system performance requirements.

With arbitrary sample rate, the user could get an almost continuous range of sample rates from 24 kHz to 61.44 MHz except for some

“dead zones” due to internal clocking constraints. This is achieved through adjusting the internal CLK PLL frequency as well as a flexible

arrangement of decimators.

DC OFFSET

The ADRV9001 receiver supports both IF down conversion and ZIF down conversion. The source of the DC offset is mainly from the

receiver LO leakage caused by the finite isolation between the LO and RF ports of a mixer, which is typical for silicon-based ICs. It could

generate a high DC component at the center of the desired signal band especially for ZIF operation. Through the datapath, the induced

dc offset is amplified and could reduce the ADC dynamic range significantly. In addition to receiver LO leakage, the device mismatch in

LPF and ADC also contributes to the DC offset problem. Without properly correcting the DC offset, it could cause a negative impact on

the system performance.

In ADRV9001, a two-step approach is taken to estimate and correct the DC offset. The first step comprises of an DC estimation step in

the digital domain and a correction procedure in the analog domain. The second step is an all-digital DC offset estimation and correction

technique that estimates and corrects for any residual DC offset after the first step.

QEC

In an ideal analog mixer, the in-phase (I) and quadrature-phase (Q) sinusoidal signals are orthogonal. In addition, the I and Q path of

LPF and ADC should have identical frequency responses. However, in reality, IQ imbalance always exists in the mixer, LPF and ADC,

resulting in quadrature errors. Without properly handling it, it seriously degrades the reception performance. For IF reception, the

respective image mixes partially onto the desired signal during the IF down conversion. In direct conversion reception, IQ-imbalance

leads to a distortion of the IQ-signals themselves within the respective desired baseband channel.

In general, quadrature error can be classified as frequency independent error (FIE) and frequency dependent error (FDE). FIE is mainly

caused by the mixer I/Q sinusoid mismatch in both gain and phase, while FDE is mainly caused by the inconsistent filter responses.

Loading...

Loading...