Preliminary Technical Data UG-1828

Rev. PrB | Page 267 of 277

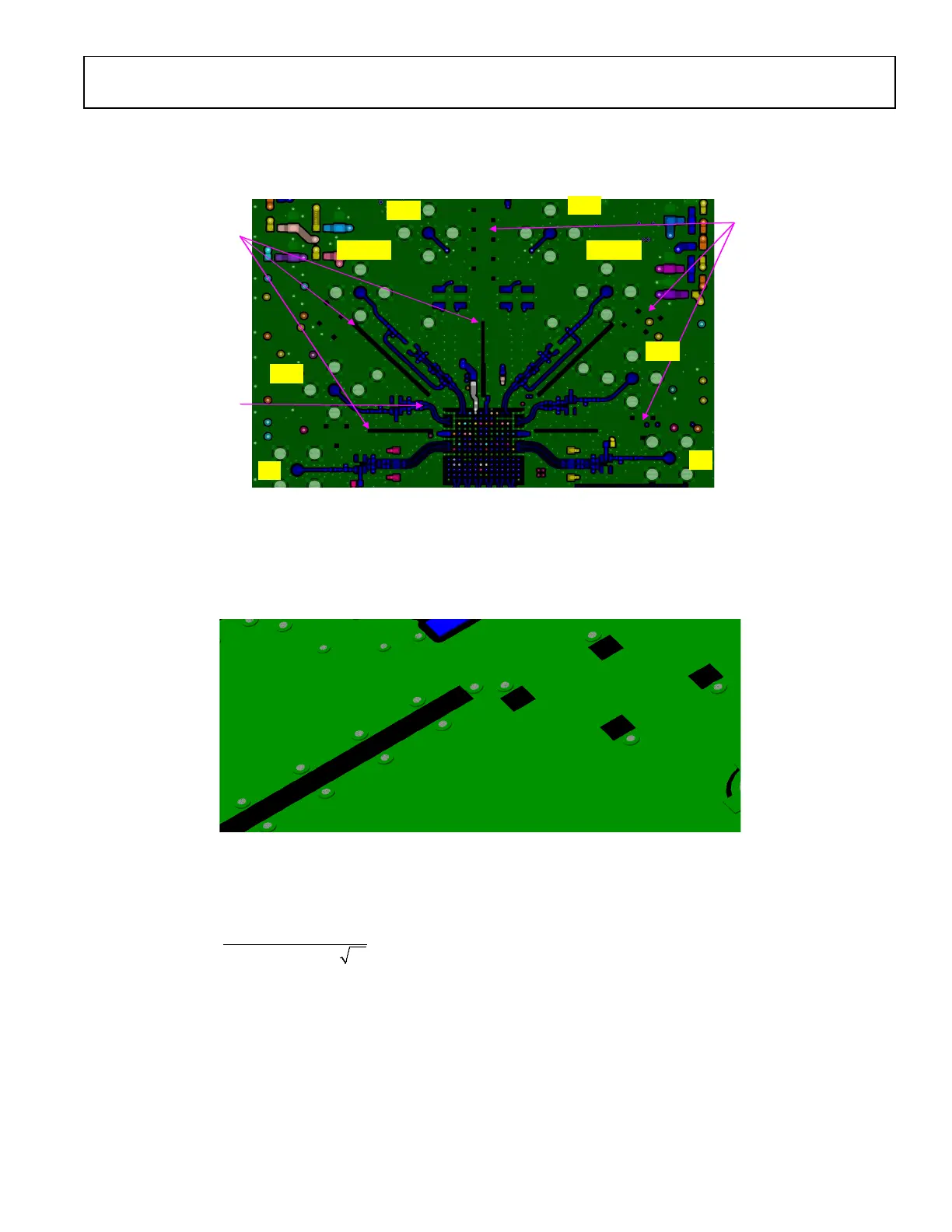

PRIMARY DEASSERT TIME

PRIMARY ASSERT TIME

PRIMARY DEASSERT TIME

PRIMARY ASSERT TIME

SECONDARY DEASSERT TIME

SECONDARY DEASSERT TIME

SECONDARY DEASSERT TIME

SECONDARY ASSERT TIME

24159-320

Figure 260. TDD Frame Timing Illustration

Note: as of v0.7.0, user should use predefined values for TDD configurations, use of custom values may cause exception.

Table 104. TDD Signals

Signal Description

RX1 Pin

TX1 Pin

RX2 Pin

TX2 Pin

These signals are hardwired to the Rx/Tx ENABLE pins (used as

SETUP signals in FH)

ORX1 Pin

ORX2 Pin

This can be used as ORX enable signal when routed to the GPIO

assigned as ORX control

RX1 DMA

RX2 DMA

TX1 DMA

TX2 DMA

ORX1 DMA

ORX2 DMA

The DMA enables that gate data transfer for each of the channels

RX1 DMA Trigger

RX2 DMA Trigger

TX1 DMA Trigger

TX2 DMA Trigger

ORX1 DMA Trigger

ORX2 DMA Trigger

These signals can be configured as triggers for the DMAs to signify

that data transfer on that channel should only occur when the

trigger signal has pulsed high followed by the DMA signal for that

channel going high.

SMA1 Trigger

Hardwired to dedicated SMA (J67) on the ZC706 board, this signal

can be used to trigger external equipment

SMA2 Trigger

Hardwired to dedicated SMA (J68) on the ZC706 board, this signal

can be used to trigger external equipment

General Purpose 1/ Hop Pin

General Purpose signal that can be routed to GPIO pins. This is also

used as the Hop Pin in FH mode.

General purpose signals that can be routed to GPIO pins as needed

Loading...

Loading...