GR740-UM-DS, Nov 2017, Version 1.7 170 www.cobham.com/gaisler

GR740

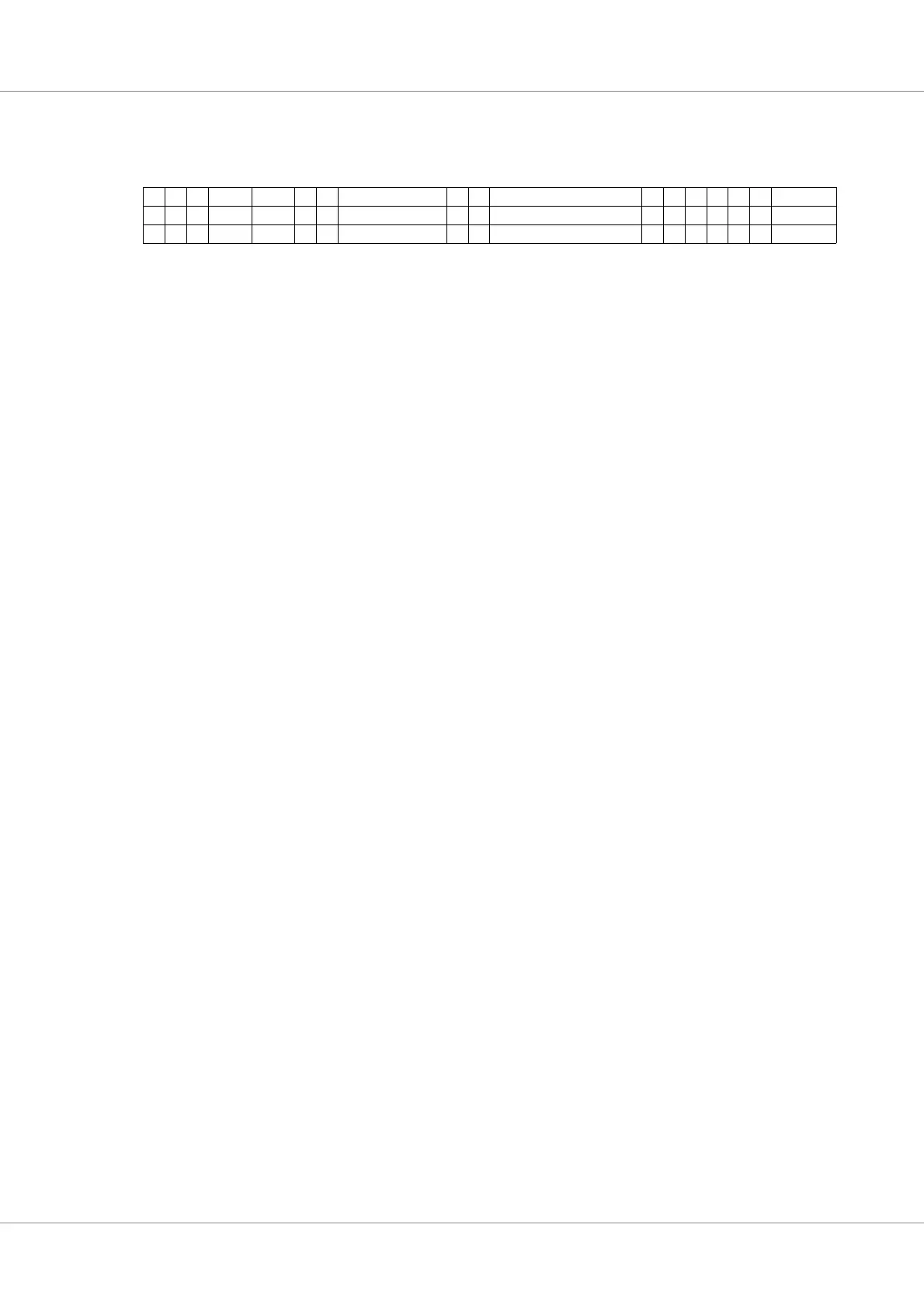

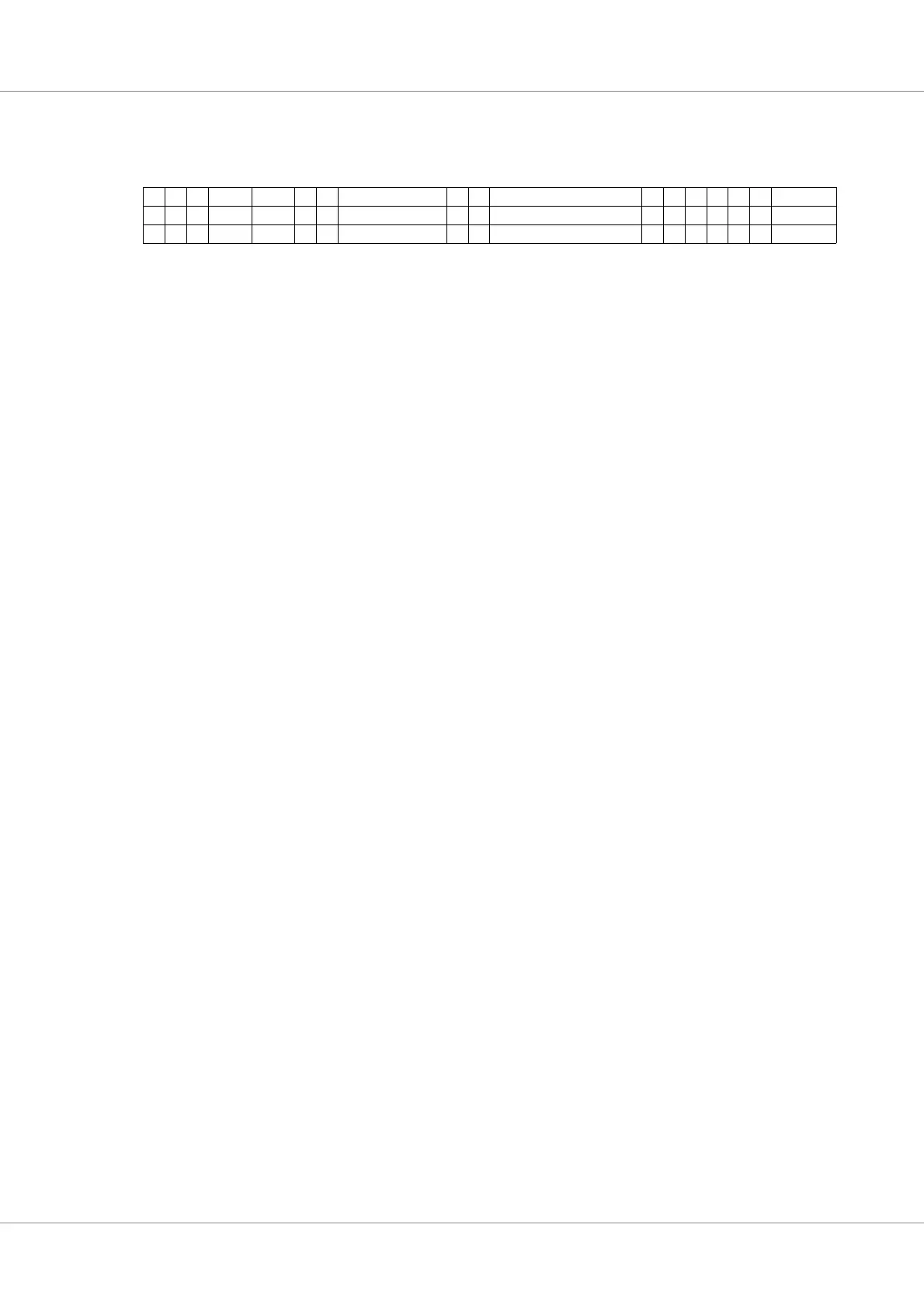

Table 155. 0x00 - RTR.AMBACTRL - AMBA port Control

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RA RX RC NCH RES DI ME RESERVED RD RE RESERVED TQ R RS PM TI IE RESERVED

111 0x3 0x0 10 0x00 01 0x00 000000 0x0

r r r r r r rw r rwrw r rw r rwrwrwrw r

31 RMAP available (RA) - Constant value of 1, indicating that the RMAP target is implemented.

30 RX unaligned access (RX) - Constant value of 1, indicating that unaligned writes are available for the receiver.

29 RMAP CRC available (RC) - Constant value of 1, indicating that RMAP CRC is enabled.

28: 27 Number of DMA channels (NCH) - The number of available DMA channels minus one. Constant value of 0x3.

26: 25 RESERVED

24 Distributed interrupt support (DI) - Constant value of 1, indicating that distributed interrupts are supported.

23 Memory error truncation enable (ME) - If set to 1, a packet being transmitted will be truncated with an EEP if an

error occur while reading from the AMBA port’s TX FIFO.

22: 18 RESERVED

17 RMAP buffer disable (RD) - If set only one RMAP buffer is used. This ensures that all RMAP commands will

be executed consecutively.

16 RMAP Enable (RE) - Enable RMAP target.

15: 9 RESERVED

8 Tick-out IRQ (TQ) - Generate interrupt when a valid time-code is received if the time-code also matches the

time-code filter specified by the RTR.AMBATIME.TCMSK and RTR.AMBATIME.TCVAL fields.

7 Time-code tick-out enable (TO) - If set to 1, the internal tickout signal is set when a valid time-code is received.

if the time-code also matches the time-code filter specified by the RTR.AMBATIME.TCMSK and RTR.AMBA-

TIME.TCVAL fields. The internal tickout signal is connected to the timer units as described in section 5.9 and in

the LATCHCFG register description in section 20.3.

6 Reset (RS) - Make complete reset of the SpaceWire node. Self clearing.

5 Promiscuous Mode (PM) - Enable Promiscuous mode.

4 Tick In (TI) - The host can generate a tick by writing a one to this field. This will increment the timer counter

and the new value is transmitted after the current character is transferred. A tick can also be generated by assert-

ing the tick_in signal.

3 Interrupt Enable (IE) - If set, an interrupt is generated when bit 8 is set and its corresponding event occurs.

2: 0 RESERVED

Loading...

Loading...