GR740-UM-DS, Nov 2017, Version 1.7 193 www.cobham.com/gaisler

GR740

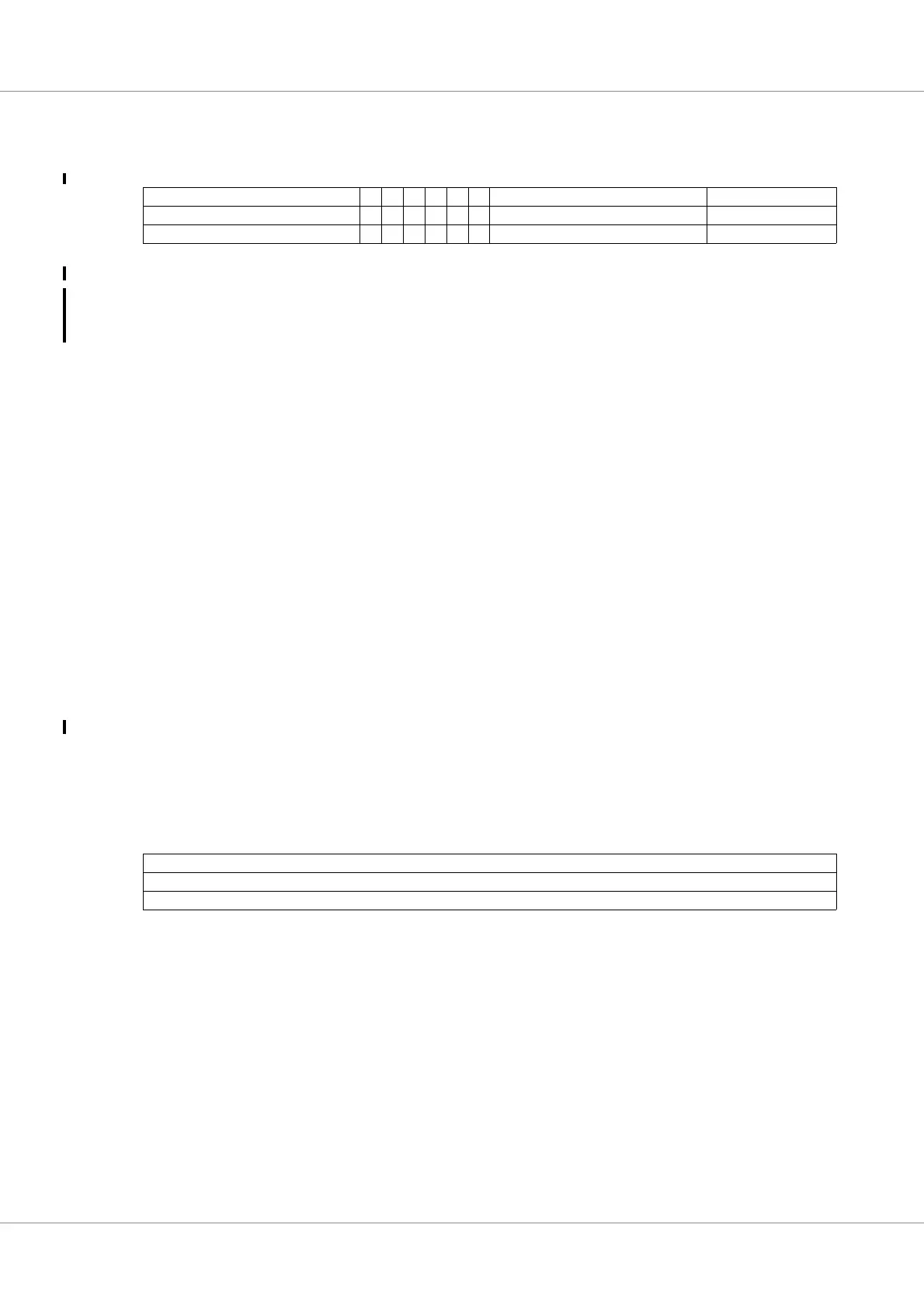

Table 193. 0x00000A24 - RTR.ICODEGEN - Interrupt code generation

31 22 21 20 19 18 17 16 15 6 5 0

RESERVED HI UA AH IT TE EN RESERVED IN

0x000 0 0 0 0 1 0 0x000 0x00

r rw* rw rw rw rw rw r rw

0

31: 22 RESERVED

21 AMBA interrupt generation (HI) - If this bit is set to 1 then an AMBA interrupt will be generated on errors/

events enabled by the fields described below.

Note: This field is only available in silicon revision 1.

20 Interrupt code generation un-acknowledge mode (UA) - If this bit is set to 1, an ISR timeout for a distributed

interrupt that was generated by the router will clear the bits in the RTR.PIP register that were set when the inter-

rupt was generated. If this bit is set to 0, no extra handling is done on an ISR timeout event, and the bits in

RTR.PIP will stay set. See section 13.2.18.

19 Interrupt acknowledgment code handling (AH) - When set to 1, and the router has generated an interrupt code, a

received interrupt acknowledgment code with the interrupt number matching the RTR.ICODEGEN.IN field will

clear the bits in the RTR.PIP register that were set when the interrupt code was generated. If set to 0, no extra

handling of a received interrupt acknowledgment code is done and the bits in RTR.PIP will stay set. This bit is

unused when the distributed interrupts are operating in the extended interrupt mode. See section 13.2.18.

18 Interrupt type (IT) - 0 = Level. 1 = Edge. When set to 0, a new interrupt code is distributed as long as RTR.PIP

register is non zero. When set to 1, a new interrupt code is distributed only when a bit in RTR.PIP toggles from

0 to 1. See section 13.2.18.

17 Interrupt acknowledgment code to interrupt code timer enable (TE) - If set to 1, the router will wait for the time

period specified by the RTR.AITIMER register after the reception of an interrupt acknowledgement code (for

which the router generated the corresponding interrupt code) until a new interrupt code is allowed to be gener-

ated. If set to 0, the timer is not used, and a new interrupt code is allowed to be generated as soon as the interrupt

acknowledgment code has been distributed.

16 Interrupt code generation enable (EN) - When 1, interrupt code generation is enabled, and an interrupt code can

be distributed when an internal error event occurs. See section 13.2.18.

15: 6 RESERVED

5: 0 Interrupt number (IN) - Sets the interrupt identifier of the interrupt code that will be distributed when the inter-

rupt code generation feature is enabled (RTR.ICODEGEN.EN = 1). See section 13.2.18.

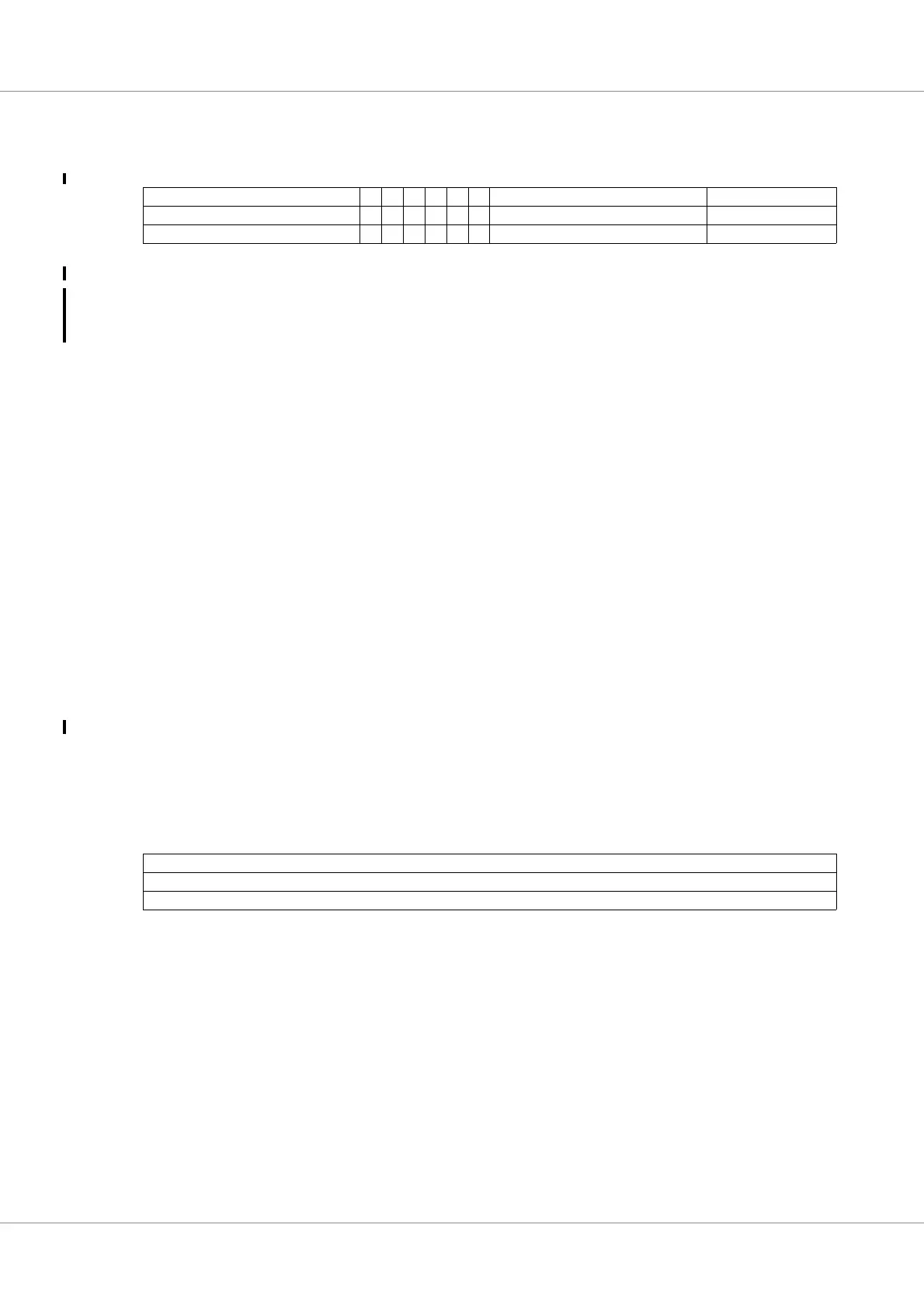

Table 194. 0x00000A28 - RTR.ISR0 - Interrupt code distribution ISR register, interrupt 0-31

31 0

IB

0x00000000

wc

31: 0 Distributed interrupt code ISR bits (IB) - The current value of the interrupt code distribution ISR register for

interrupt numbers 0 - 31. Each bit index corresponds to the ISR bit value for the corresponding interrupt number.

A bit value of 1 indicates that an interrupt code with the corresponding interrupt number has been received, but

not yet acknowledged. A bit value of 0 indicates either that no interrupt code with the corresponding interrupt

number has been received, or that the previous interrupt code was either acknowledged or timed out. This regis-

ter should be normally only be used for diagnostics and / or FDIR.

Loading...

Loading...