GR740-UM-DS, Nov 2017, Version 1.7 192 www.cobham.com/gaisler

GR740

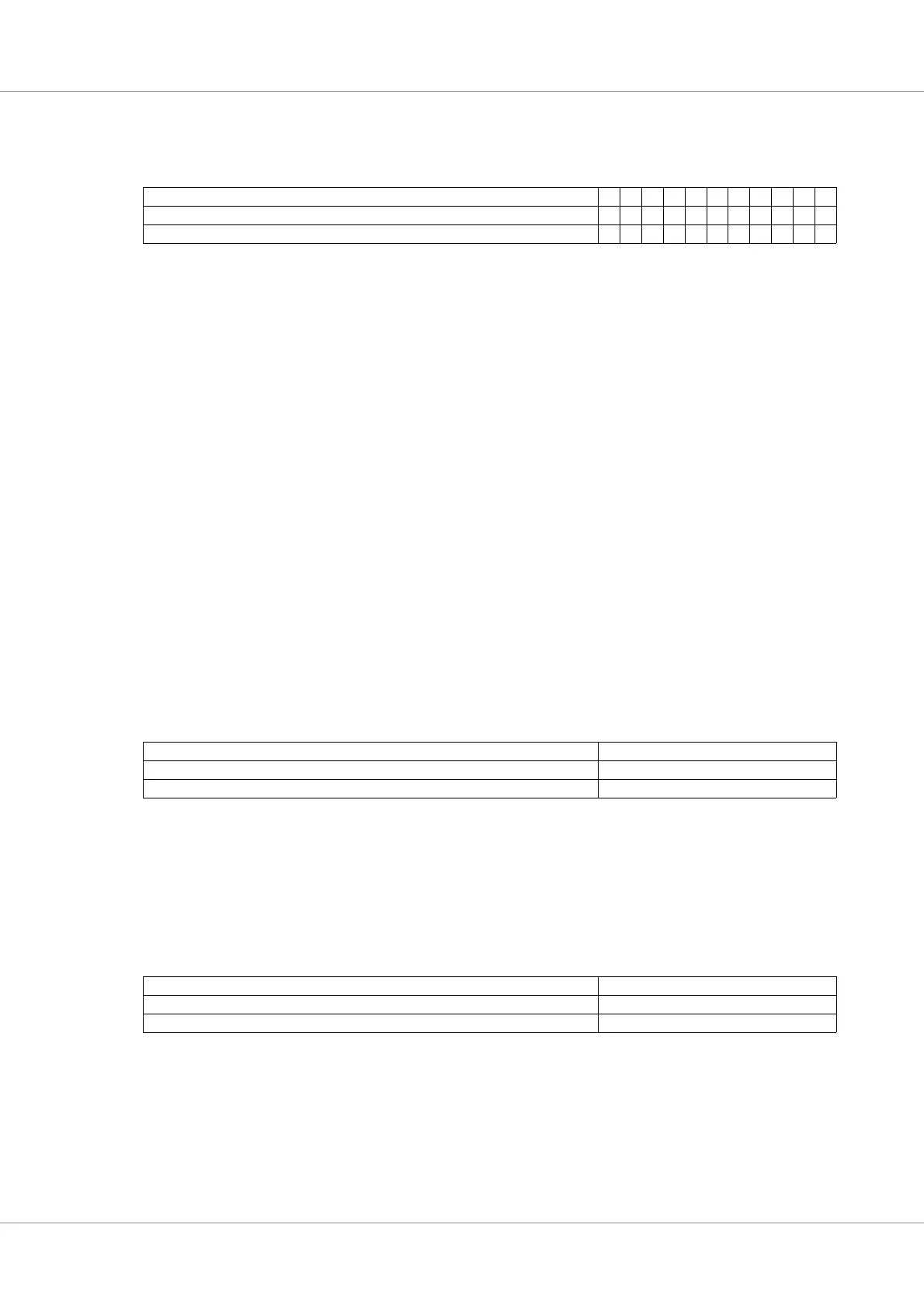

Table 190. 0x00000A18 - RTR.IMASK - Interrupt mask

31 11109876543210

RESERVED PESRRSTT PL TSACRE IA LEME

0x00000 0 0 0 0 0 0 0 0 0 0 0

r rwrwrwrwrwrwrwrwrwrwrw

31: 11 RESERVED

10 SpaceWire Plug-and-Play error (PE) - Generate an interrupt when a SpaceWire Plug and Play error has been

detected in the configuration port. The different errors are described in 13.5.4.

9 Spill-if-not-ready (SR) - Generate an interrupt when a packet has been spilled because of the spill-if-not-ready

feature described in section 13.2.10.

8 Run-state entry (RS) - Generate an interrupt when a SpaceWire link enters run-state.

7 Time code / distributed interrupt code tick truncation (TT) - Generate an interrupt when a packet has been spilled

because of the time code / distributed interrupt code truncation feature described in section 13.2.21.1.

6 Packet length truncation (PL) - Generate an interrupt when a packet has been spilled due to the packet length

truncation feature described in section 13.2.16.

5 Timeout spill (TS) - Generate an interrupt when a packet has been spilled due to the timeout mechanism.

4 Auxiliary configuration port error (AC) - Generate an interrupt when either a header CRC error, protocol ID

error, packet type error, early EOP, or early EEP has been detected in the configuration port.

3 RMAP error (RE) - Generate an interrupt when an error has been detected in the configuration port for an

RMAP command such that the PSTS.EC field is set to a non-zero value.

2 Invalid address (IA)- Generate an interrupt when an invalid address error has occurred on a port. See

RTR.PSTS:IA bit and section 13.2.12 for a definition of invalid address.

1 Link error (LE) - Generate an interrupt when a link error has been detected on a SpaceWire port.

0 Memory error (ME) - Generate an interrupt when a memory error occur in any of the router’s on-chip memories.

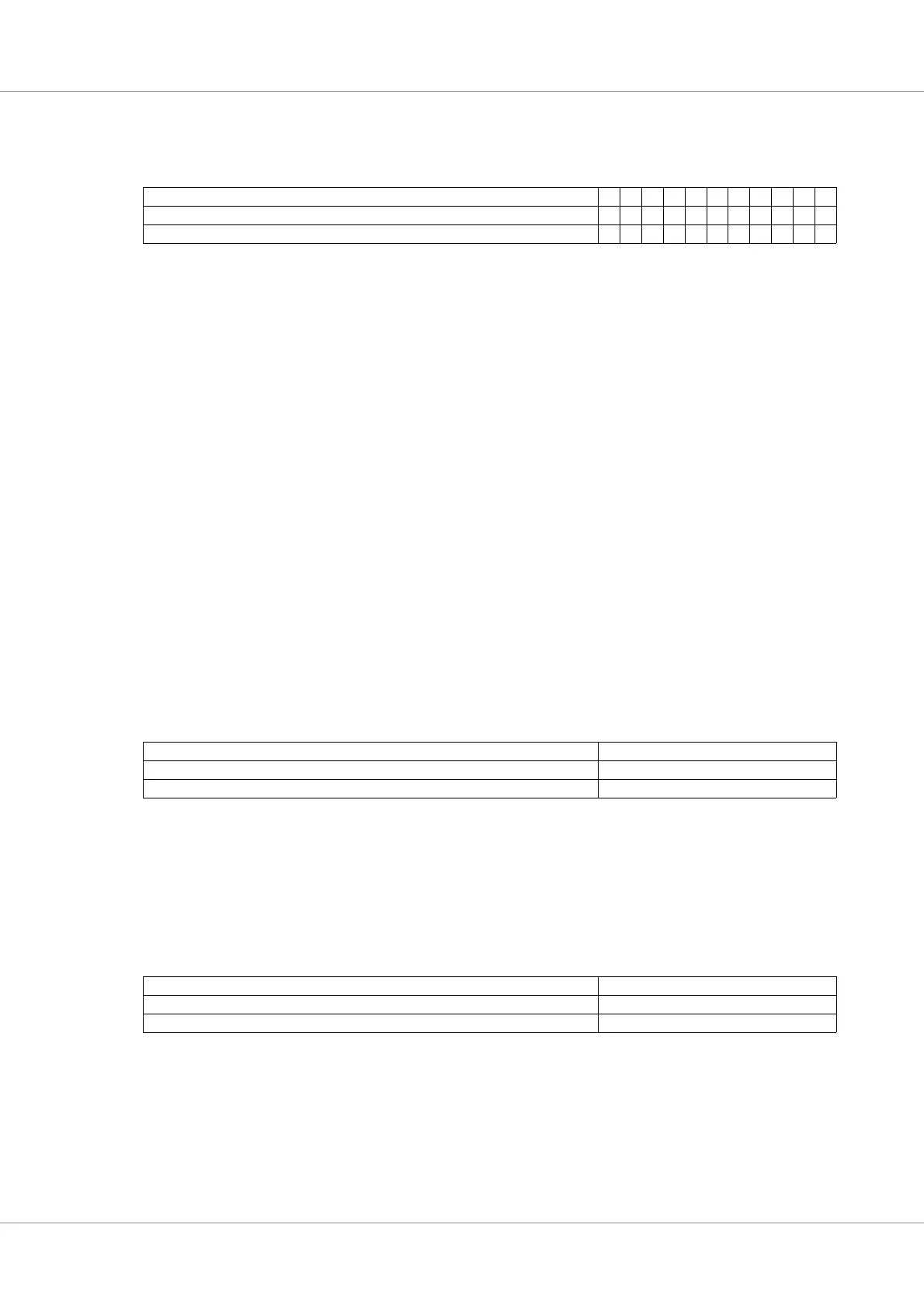

Table 191. 0x00000A1C - RTR.IPMASK - Interrupt port mask

31 13 12 0

RESERVED IE

0x000 0x0000

rrw

31: 20 RESERVED

19: 0 Port interrupt enable (IE) - Set a bit to 1 to enable interrupts to be generated for an error detected in the port with

the same number as the bit index. An interrupt is optionally signalled through a distributed interrupt code.

Table 192. 0x00000A20 - RTR.PIP - Port interrupt pending

31 13 12 0

RESERVED IP

0x000 0x0000

rwc

31: 20 RESERVED

19: 0 Interrupt pending (IP) - When a bit is set to 1, the port with the same number as the bit index was the source of

an interrupt. A bit in this field will only be set to 1 for a generated interrupt if the port’s corresponding bit in

RTR.IPMASK is set, as well as the error types corresponding bit in RTR.IMASK, are set.

Loading...

Loading...