GR740-UM-DS, Nov 2017, Version 1.7 309 www.cobham.com/gaisler

GR740

21.3.5 Multiprocessor status register

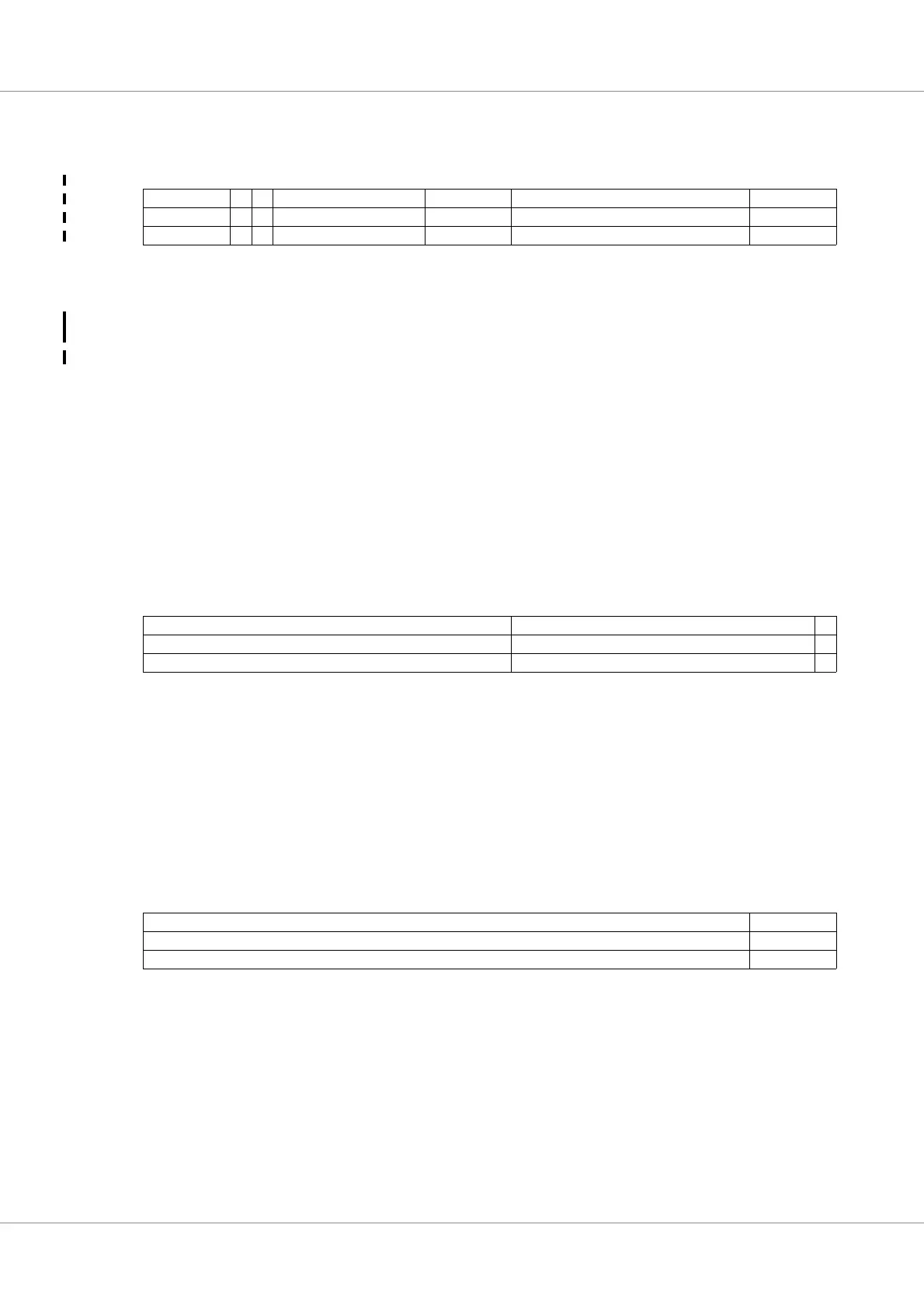

Table 383.0x010 - MPSTAT - Multiprocessor status register

21.3.6 Broadcast register

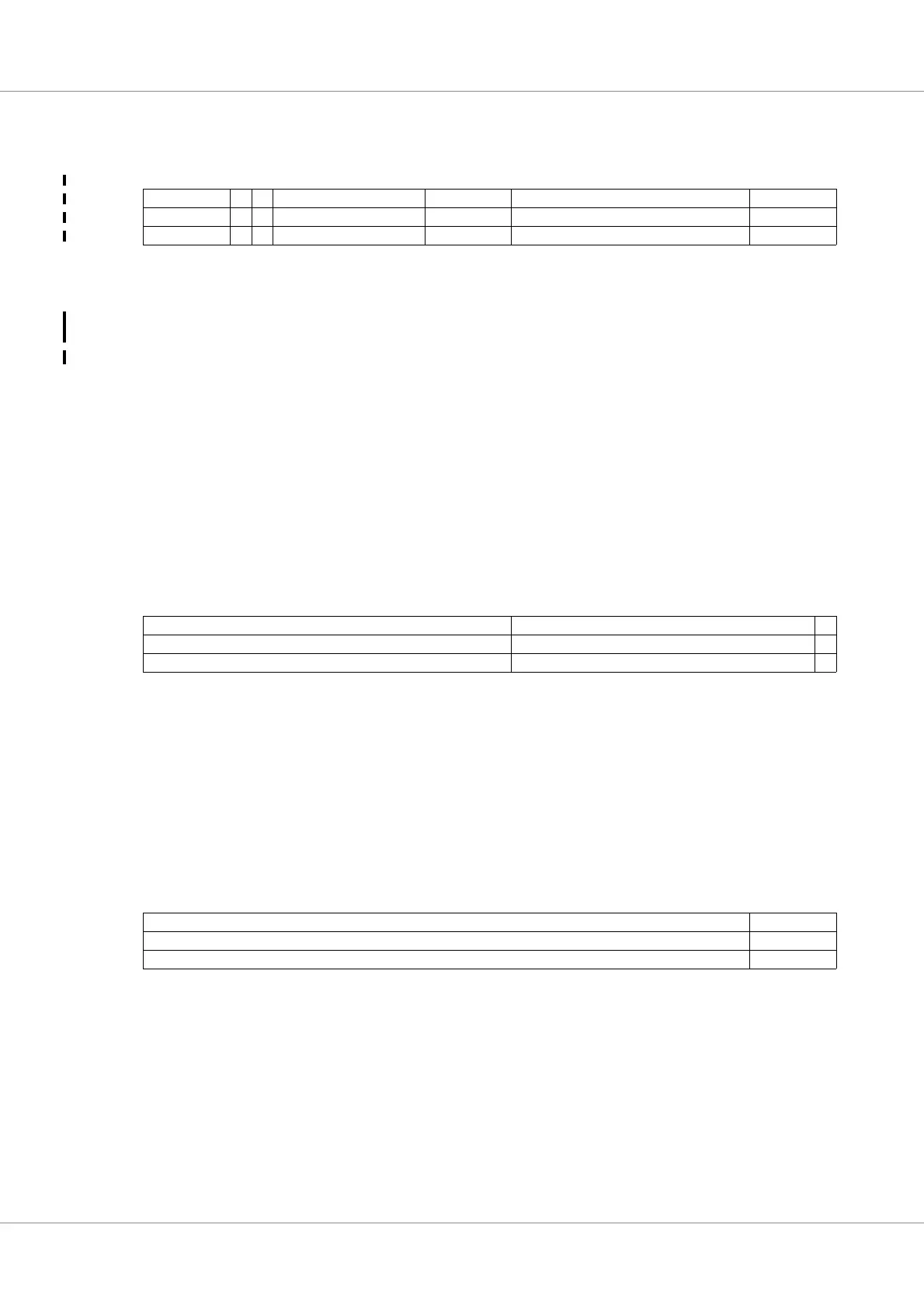

Table 384.0x014 - BRDCST - Broadcast register

21.3.7

Table 385.0x018 - ERRSTAT - Error Mode Status Register

Error Mode Status Register

Note:

This register is only available in GR740 silicon revision 1. See section 43.2.12.

31 28 27 26 25 20 19 16 15 4 3 0

NCPU BA ER RESERVED EIRQ RESERVED STATUS

31* 0 0xA 0 *

rrr r r r rw

31: 28 Number of CPUs (NCPU) - Number of CPUs in the system - 1

27 Broadcast Available (BA) - Set to ‘1’ if NCPU > 0.

26 Extended boot registers available (ER) - Set to ‘0’ in GR740 silicon revision 0 and set to ’1’ in

GR740 silicon revision ’1’.

25: 20 RESERVED

19: 16 Extended IRQ (EIRQ) - Interrupt number (1 - 15) used for extended interrupts. Fixed to 0 if

extended interrupts are disabled.

15: 4 RESERVED

3: 0 Power-down status of CPU[n] (STATUS[n]) - ‘1’ = power-down, ‘0’ = running.

Write STATUS[n] with ‘1’ to start processor n.

The reset value for this field is 0xE if the external signal BREAK is LOW. Otherwise the reset value

is 0xF.

31 16 15 1 0

RESERVED BM15:1] R

000

rrwr

31: 16 RESERVED

15: 1 Broadcast Mask n (BM[n]) - If BM[n] = ‘1’ then interrupt n is broadcasted (written to the Force Reg-

ister of all CPUs), otherwise standard semantic applies (Pending register)

0RESERVED

31 43 0

RESERVED ERRMODE[3:0]

0*

rrw

31:4 Reserved

3:0 Read: Error mode status of CPU[n] (STATUS[n]) - ‘1’ = error mode, ‘0’ = other (debug/run/power-

down).

Write: Force CPU[n] into error mode

Loading...

Loading...