GR740-UM-DS, Nov 2017, Version 1.7 311 www.cobham.com/gaisler

GR740

21.3.11 Processor interrupt mask registers

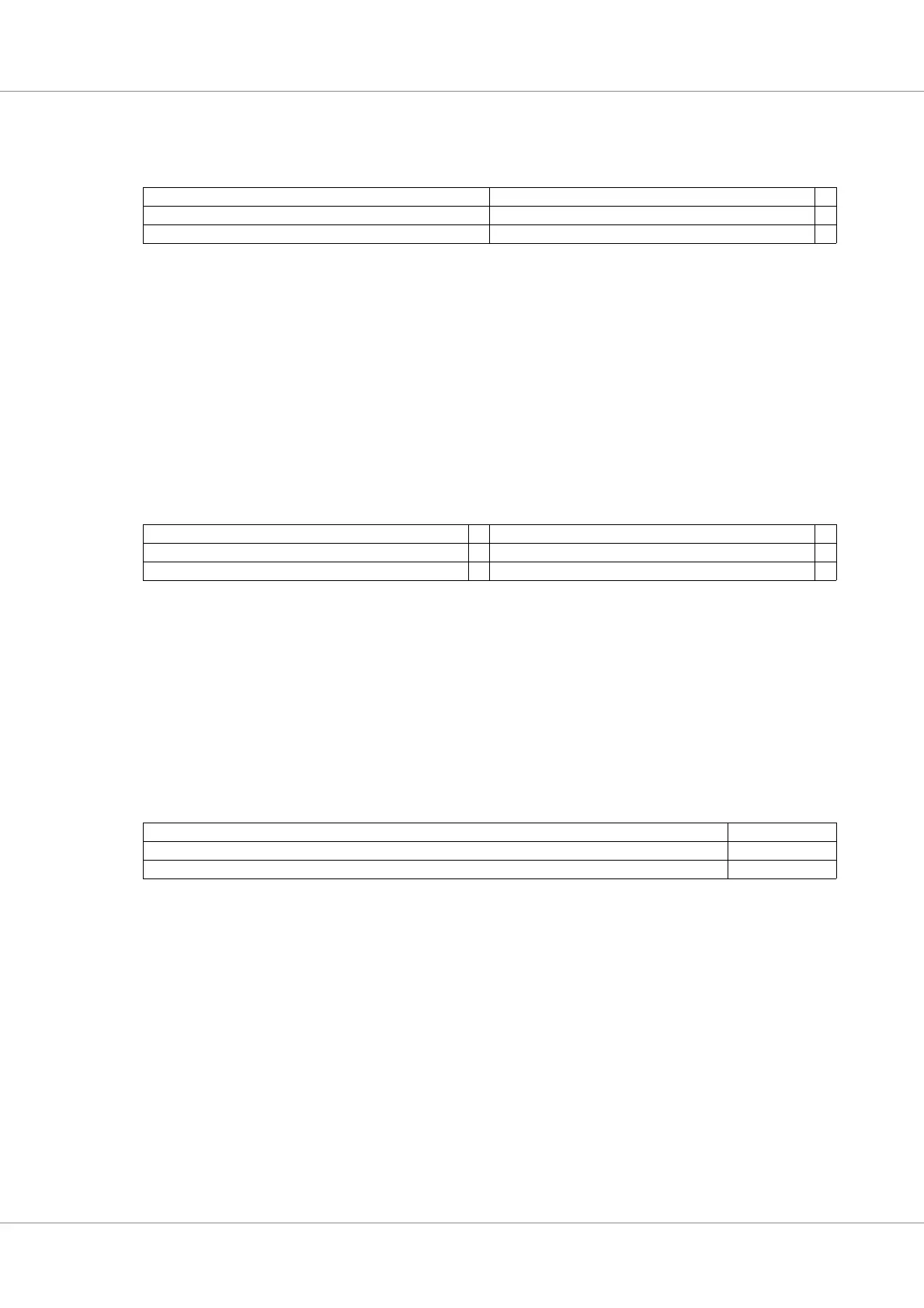

Table 389.0x040, 0x044, 0x048, 0x04C - PIMASK0-3 - Processor 0, 1, 2, 3 interrupt mask register

21.3.12 Processor interrupt force registers

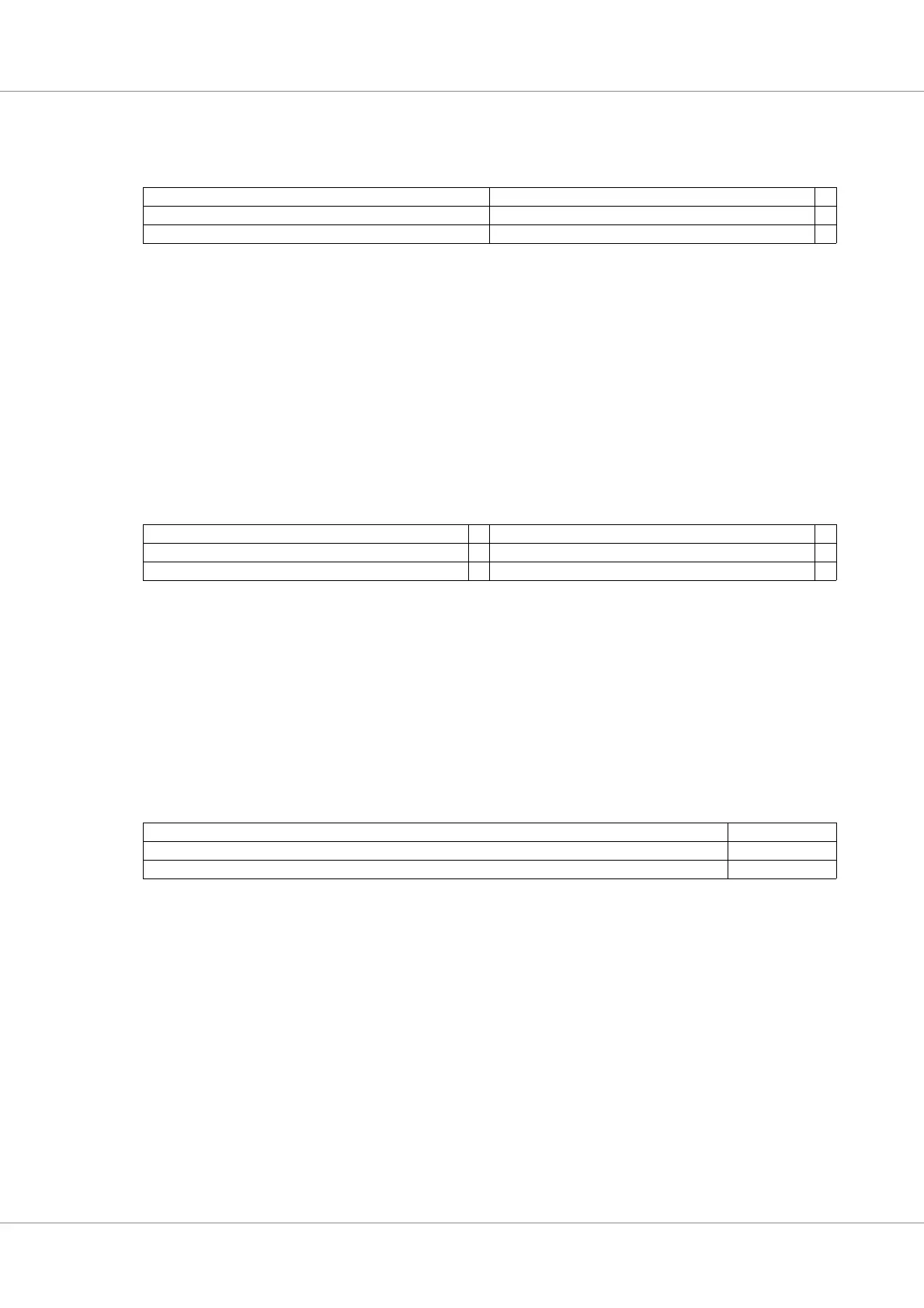

Table 390.0x080, 0x084, 0x088, 0x08C - PIFORCE0-3 - Processor 0, 1, 2, 3 interrupt force register

21.3.13 Extended interrupt acknowledge registers

Table 391.0x0C0, 0x0C4, 0x0C8, 0x0CC - PEXTACK0-3 - Processor 0, 1, 2, 3 extended interrupt acknowledge register

31 16 15 1 0

EIM[31:16] IM15:1] R

00R

rw rw r

31: 16 Extended Interrupt Mask n (EIC[n]) - Interrupt mask for extended interrupts

15: 1 Interrupt Mask n (IM[n]) - If IM[n] = ‘0’ then interrupt n is masked, otherwise it is enabled.

0RESERVED

31 17 16 15 1 0

FC[15:1] R IF15:1] R

0000

wc r rw* r

31: 17 Interrupt Force Clear n (IFC[n]) - Interrupt force clear for interrupt n. Bits can be cleared by writing

’1’ to their position, writes of ’0’ have no effect.

16 RESERVED

15: 1 Interrupt Force n (IF[n]) - Force interrupt nr n. Bits can be asserted by writing ’1’ to their position.

Writes of ’0’ have no effect.

0RESERVED

31 54 0

RESERVED EID[4:0]

00

rr

31: 5 RESERVED

4: 0 Extended interrupt ID (EID) - ID (16-31) of the most recent acknowledged extended interrupt.

Loading...

Loading...