GR740-UM-DS, Nov 2017, Version 1.7 335 www.cobham.com/gaisler

GR740

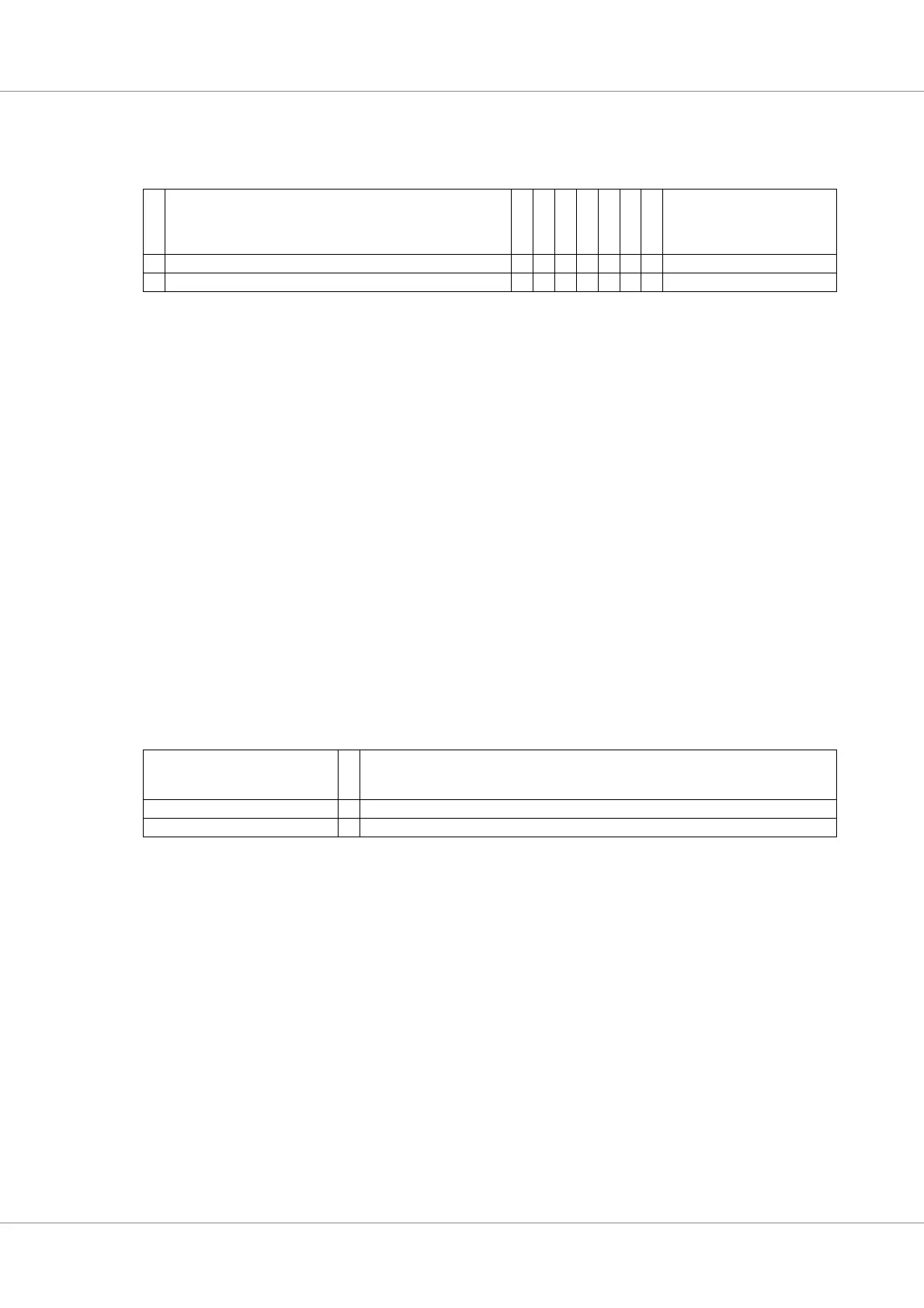

24.3.4 Mask register

Table 423.0x28 - MASK - Mask register

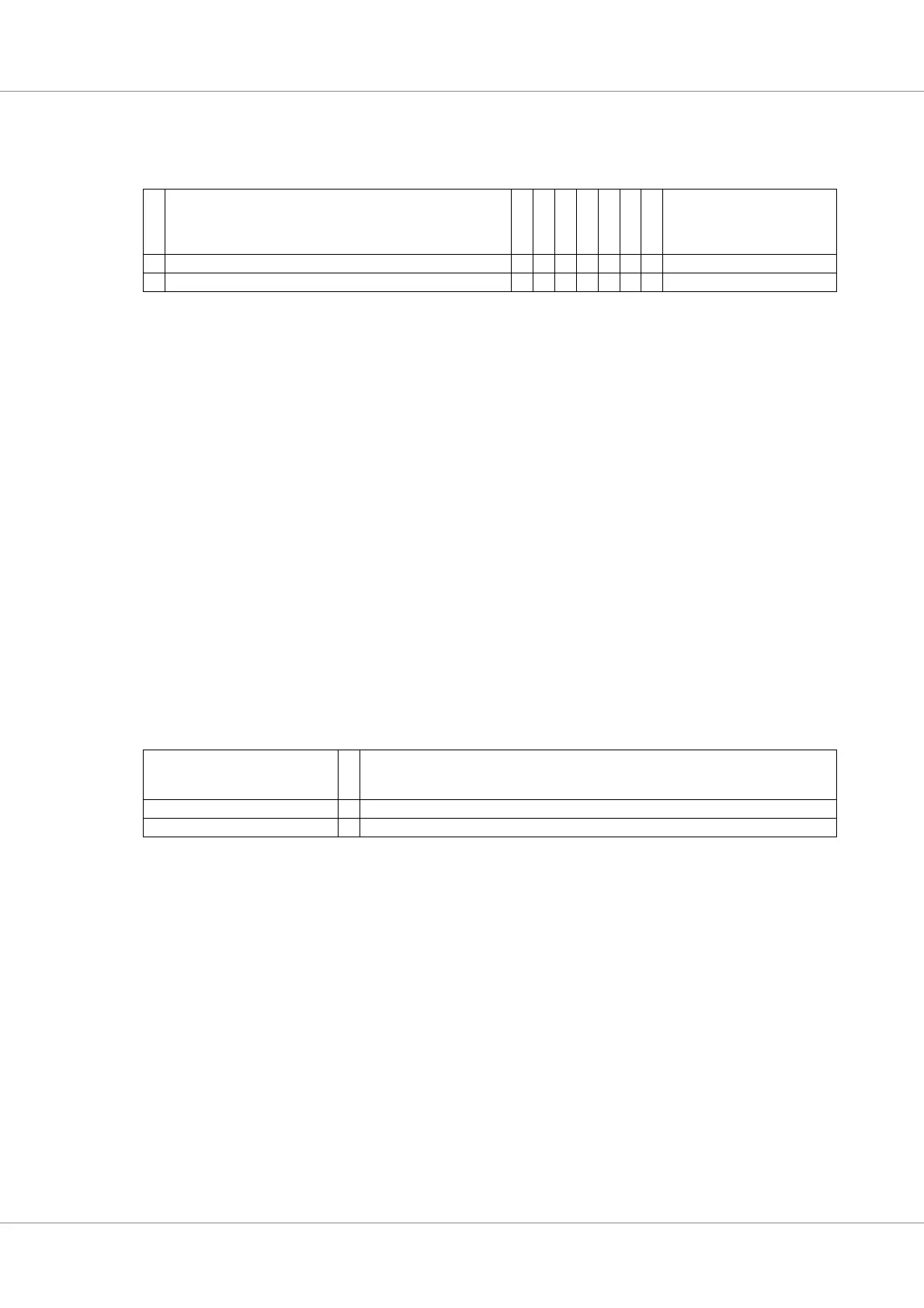

24.3.5 Command register

Table 424.0x2C - CMD - Command register

31 30 15 14 13 12 11 10 9 8 7 0

T

I

P

E

RESERVED L

T

E

RO

V

E

U

N

E

M

M

E

E

N

E

E

E

N

F

E

RESERVED

0 0 0000001 0

rw r rw r rw rw rw rw rw r

31 Transfer in progress enable (TIPE) - When this bit is set the core will generate an interrupt when the

TIP bit in the Event register transitions from ‘0’ to ‘1’.

30: 15 RESERVED (R) - Read as zero and should be written to zero to ensure forward compatibility.

14 Last character enable (LTE) - When this bit is set the core will generate an interrupt when the LT bit

in the Event register transitions from ‘0’ to ‘1’.

13 RESERVED (R) - Read as zero and should be written to zero to ensure forward compatibility.

12 Overrun enable (OVE) - When this bit is set the core will generate an interrupt when the OV bit in

the Event register transitions from ‘0’ to ‘1’.

11 Underrun enable (UNE) - When this bit is set the core will generate an interrupt when the UN bit in

the Event register transitions from ‘0’ to ‘1’.

10 Multiple-master error enable (MMEE) - When this bit is set the core will generate an interrupt when

the MME bit in the Event register transitions from ‘0’ to ‘1’.

9 Not empty enable (NEE) - When this bit is set the core will generate an interrupt when the NE bit in

the Event register transitions from ‘0’ to ‘1’.

8 Not full enable (NFE) - When this bit is set the core will generate an interrupt when the NF bit in the

Event register transitions from ‘0’ to ‘1’.

7: 0 RESERVED (R) - Read as zero and should be written to zero to ensure forward compatibility.

31 30 23 22 21

RESERVED L

S

T

RESERVED

00 0

rw r

31: 23 RESERVED (R) - Read as zero and should be written to zero to ensure forward compatibility.

22 Last (LST) - After this bit has been written to ‘1’ the core will set the Event register bit LT when a

character has been transmitted and the transmit queue is empty. If the core is operating in 3-wire

mode the Event register bit is set when the whole transfer has completed. This bit is automatically

cleared when the Event register bit has been set and is always read as zero.

21: 0 RESERVED (R) - Read as zero and should be written to zero to ensure forward compatibility.

Loading...

Loading...