GR740-UM-DS, Nov 2017, Version 1.7 442 www.cobham.com/gaisler

GR740

.

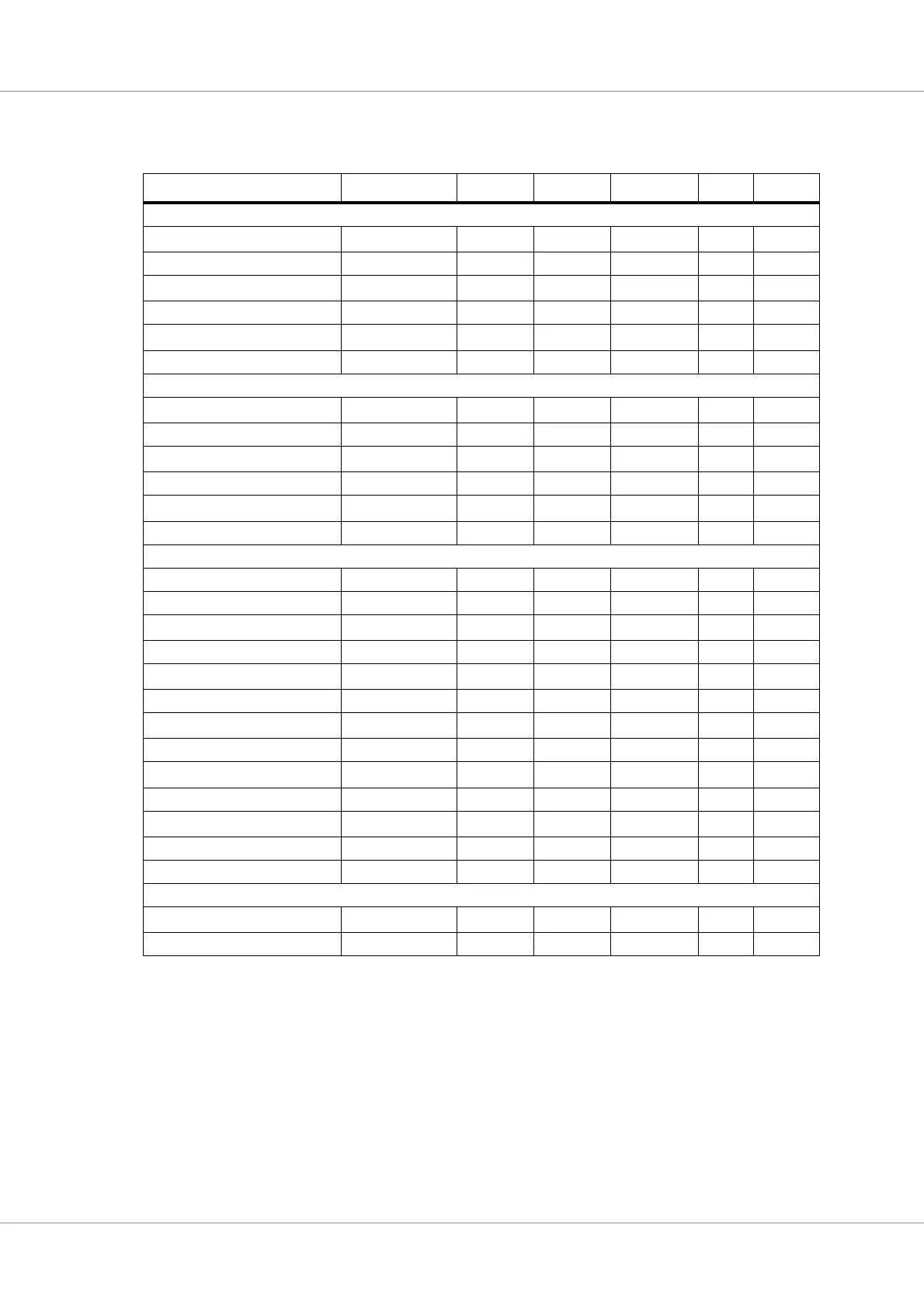

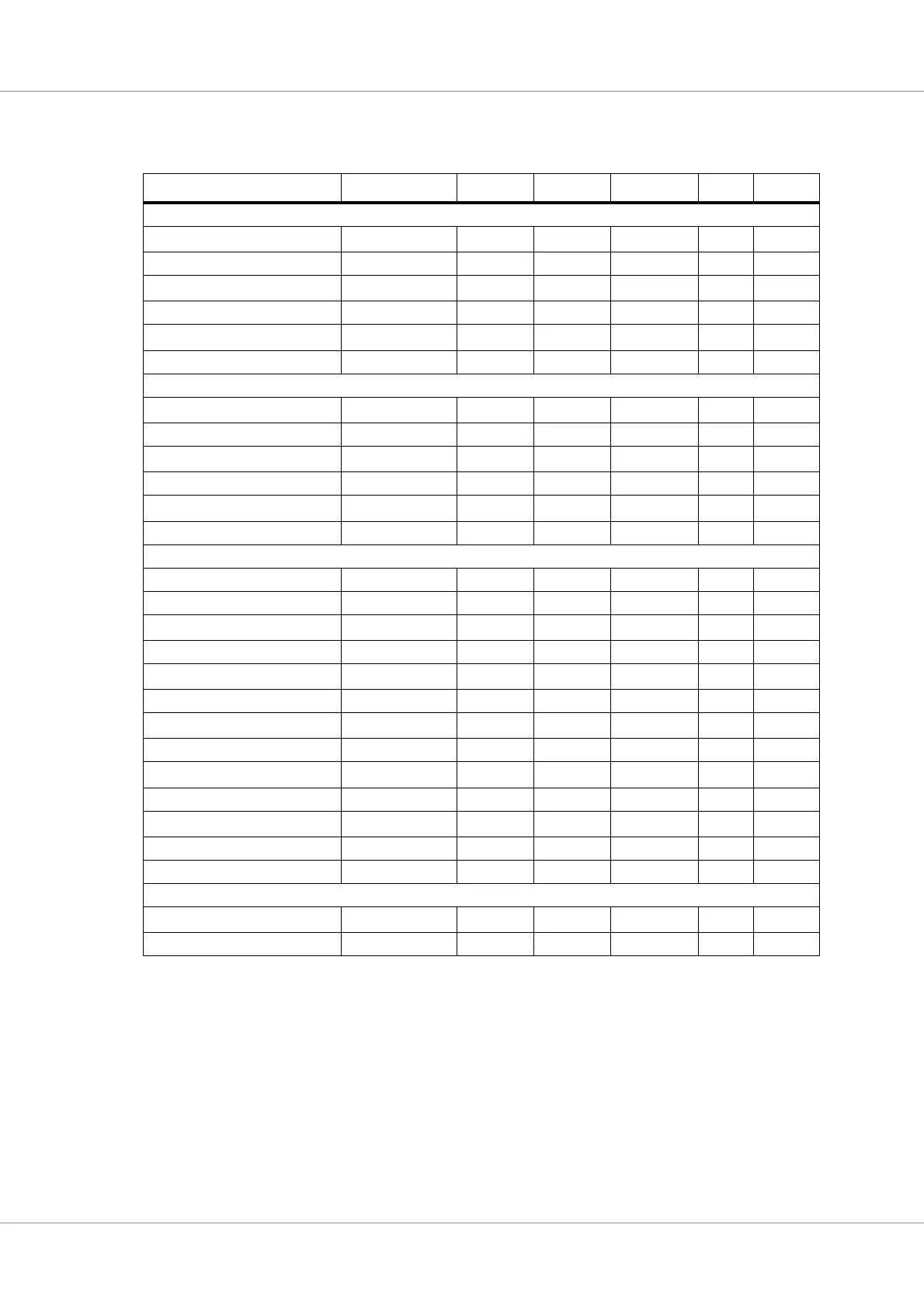

Table 579.Recommended AC operating conditions

Parameter Symbol Minimum Nominal Maximum Unit Note(s)

Externally fed PLL input clocks, PLLs enabled (in default configuration)

SYS_CLK frequency f

sys_clk

20 50 70 MHz

1

SYS_CLK duty cycle 40 50 60 %

6

SPW_CLK frequency f

spw_clk

20 50 55 MHz

1

SPW_CLK duty cycle 40 50 60 %

6

MEM_EXTCLK frequency f

mem_extclk

20 50 55 MHz

1, 2

MEM_EXTCLK duty cycle 40 50 60 %

6

Externally fed PLL input clocks, PLLs bypassed

SYS_CLK frequency f

sys_clk_bypass

0 50 100 MHz

1

SYS_CLK duty cycle 20 50 80 %

6

SPW_CLK frequency f

spw_clk_bypass

0 50 100 MHz

1

SPW_CLK duty cycle 40 50 60 %

6

MEM_EXTCLK frequency f

mem_extclk_bypass

0 100 100 MHz

1, 2

MEM_EXTCLK duty cycle 20 50 80 %

6

External fed clocks, non-PLL

MEM_CLK_IN frequency 0 100 100

MEM_CLK_IN duty cycle 20 50 80 %

6

PCI_CLK frequency f

pci_clk

33 33 33 MHz

3

PCI_CLK duty cycle 20 50 80 %

6

ETH*_GTXCLK frequency f

eth_gtxclk

125 125 125 MHz

ETH*_GTXCLK duty cycle 40 50 60 %

6

ETH*_TXCLK frequency f

eth_txclk

25 25 25 MHz

ETH*_TXCLK duty cycle 20 50 80 %

6

ETH*_RXCLK frequency f

eth_rxclk

25 25 or 125 125 MHz

ETH*_RXCLK duty cycle 40 50 60 %

6

GR1553_CLK frequency f

gr1553_clk

19.999 20 20.001 MHz

GR1553_CLK duty cycle 20 50 80 %

6

GR1553_CLK jitter 5 ns

6, 7

Internally generated clocks

AMBA system clock frequency f

soc_system

40 250 250 MHz

4, 5

Internal SPW clock frequency 10 400 400 MHz

1

Min/max values are maximum for on-chip PLL input, limits for the generated frequencies must also be satisfied.

Nominal frequency required for correct operation with PLL power-up configuration and will change if reconfigured.

2

Assuming MEM_CLKSEL has been set high so that MEM_EXTCLK is used

3

The PCI interface will not be fully compliant to the PCI specification. Interface will be characterised at a later date.

4

The minimum clock frequency for the on-chip system is determined by functional interface limitations and has not

been fully characterised. A clock frequency over 40 MHz is required for the Ethernet interfaces to function at gigabit

speeds.

5

The maximum given here is from static timing analysis in worst case PVT corner and includes margins for aging and

jitter, and it is also used as clock rate during production tests.

6

Supplied as design parameter, not tested

7

Limit on rising edge only

Loading...

Loading...