Titanium Interfaces User Guide

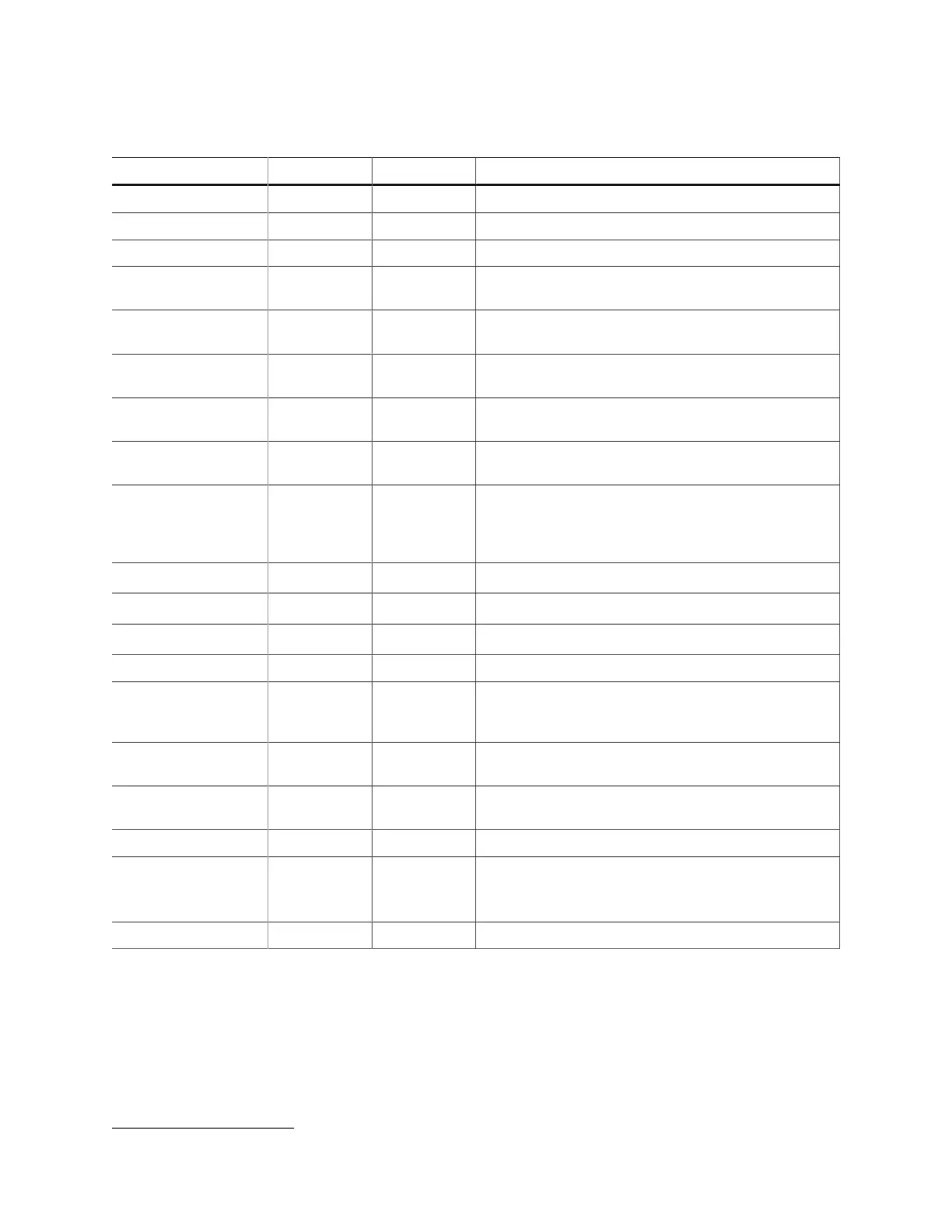

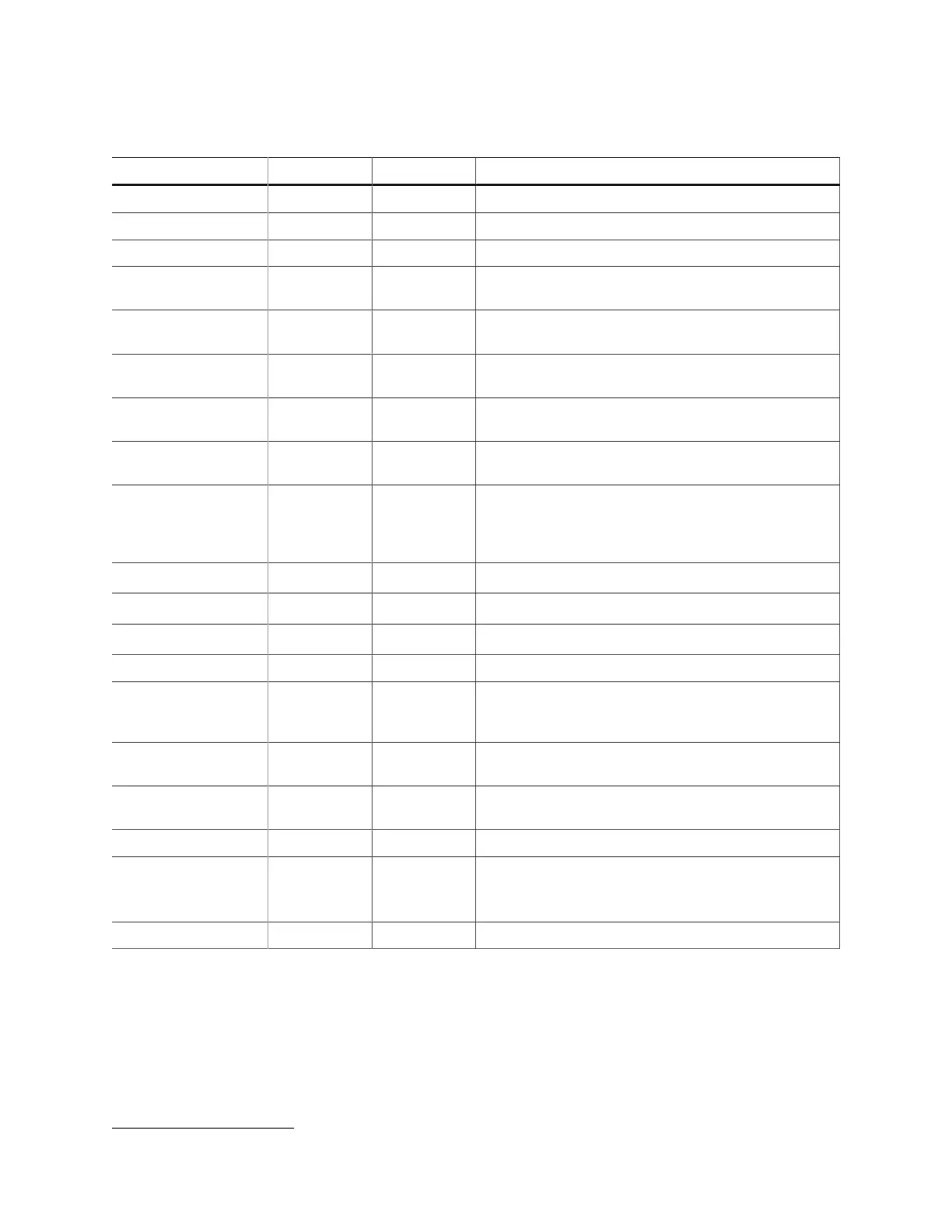

Table 50: MIPI RX Lane Signals

Interface to MIPI soft CSI/DSI controller with D-PHY in FPGA Fabric

Signal Direction Clock Domain Description

HS_IN[7:0] Output SLOWCLK High-speed parallel data input.

LP_P_IN Output – Low-power input data from the P pad.

LP_N_IN Output – Low-power input data from the N pad.

LP_P_OUT Input – (Optional) Low-power output data from the core for the

P pad. Used if the data lane is reversible.

LP_N_OUT Input – (Optional) Low-power output data from the core for the

N pad. Used if the data lane is reversible.

FIFO_EMPTY Output FIFOCLK (Optional) When the FIFO is enabled, this signal

indicates that the FIFO is empty.

SLOWCLKOUT

(6)

Output – Divided down parallel (slow) clock from the pads. Can

only drive RX DATA lanes.

FASTCLKOUT

(6)

Output – Serial (fast) clock from the pads. Can only drive RX

DATA lanes.

CLKOUT Output – Divided down parallel (slow) clock from the pads that

can drive the core clock tree. Used to drive the core

logic implementing the rest of the D-PHY protocol. It

should also connect to the FIFOCLK of the data lanes.

SLOWCLK

(6)

Input – Parallel (slow) clock.

FASTCLK

(6)

Input – Serial (fast) clock.

FIFOCLK

(6)

Input – (Optional) Core clock to read from the FIFO.

FIFO_RD Input FIFOCLK (Optional) Enables FIFO to read.

RST Input FIFOCLK

SLOWCLK

(Optional) Asynchronous. Resets the FIFO and

serializer. If the FIFO is enabled, it is relative to

FIFOCLK; otherwise it is relative to SLOWCLK.

HS_ENA Input – Dynamically enable the differential input buffer when in

high-speed mode.

HS_TERM Input – Dynamically enables input termination high-speed

mode.

DLY_ENA Input SLOWCLK (Optional) Enable the dynamic delay control.

DLY_INC Input SLOWCLK (Optional) Dynamic delay control. When DLY_ENA is 1,

1: Increments

0: Decrements

DLY_RST Input SLOWCLK (Optional) Reset the delay counter.

(6)

These signals are in the primitive, but the software automatically connects them for you.

www.efinixinc.com 96

Loading...

Loading...