22 www.xilinx.com Virtex-4 FPGA Configuration User Guide

UG071 (v1.12) June 2, 2017

Chapter 1: Configuration Overview

“Configuration Interfaces” for important startup option guidelines. By default, startup

events occur as shown in Table 1-9.

The start-up sequence can be forced to wait for the DCMs to lock or for DCI to match with

the appropriate BitGen options. These options are typically set to prevent DONE, GTS, and

GWE from being asserted (preventing device operation) before the DCMs have locked

and/or DCI has matched.

The DONE signal is released by the start-up sequencer on the cycle indicated by the user,

but the start-up sequencer does not proceed until the DONE pin actually sees a logic High.

The DONE pin is an open-drain bidirectional signal by default. By releasing the DONE

pin, the device simply stops driving a logic Low and the pin goes into a high-Z state. An

external pull-up resistor is needed for the DONE pin to reach a logic High in this case.

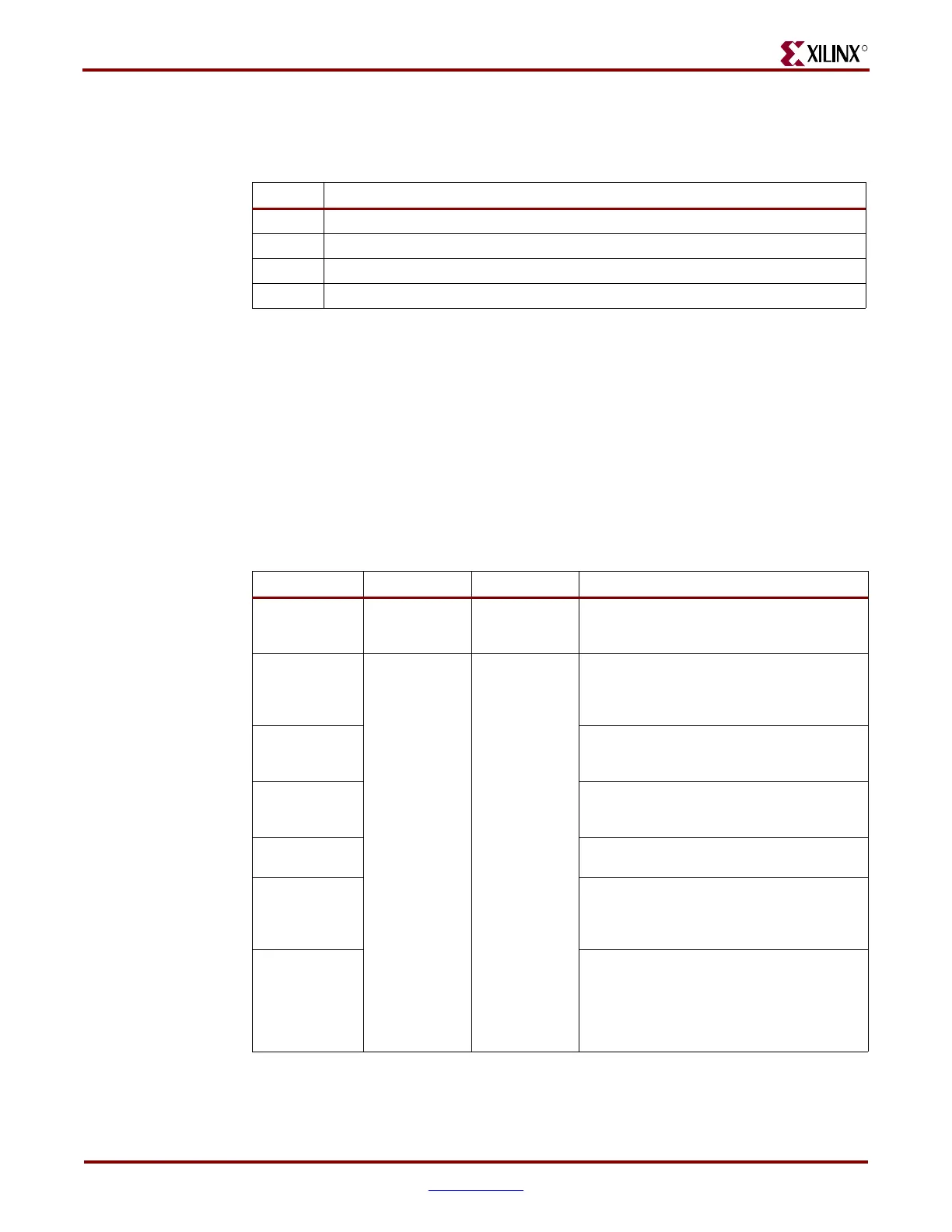

Table 1-10 shows signals relating to the status register. Figure 1-11 shows the signals

relating to the start-up sequencer.

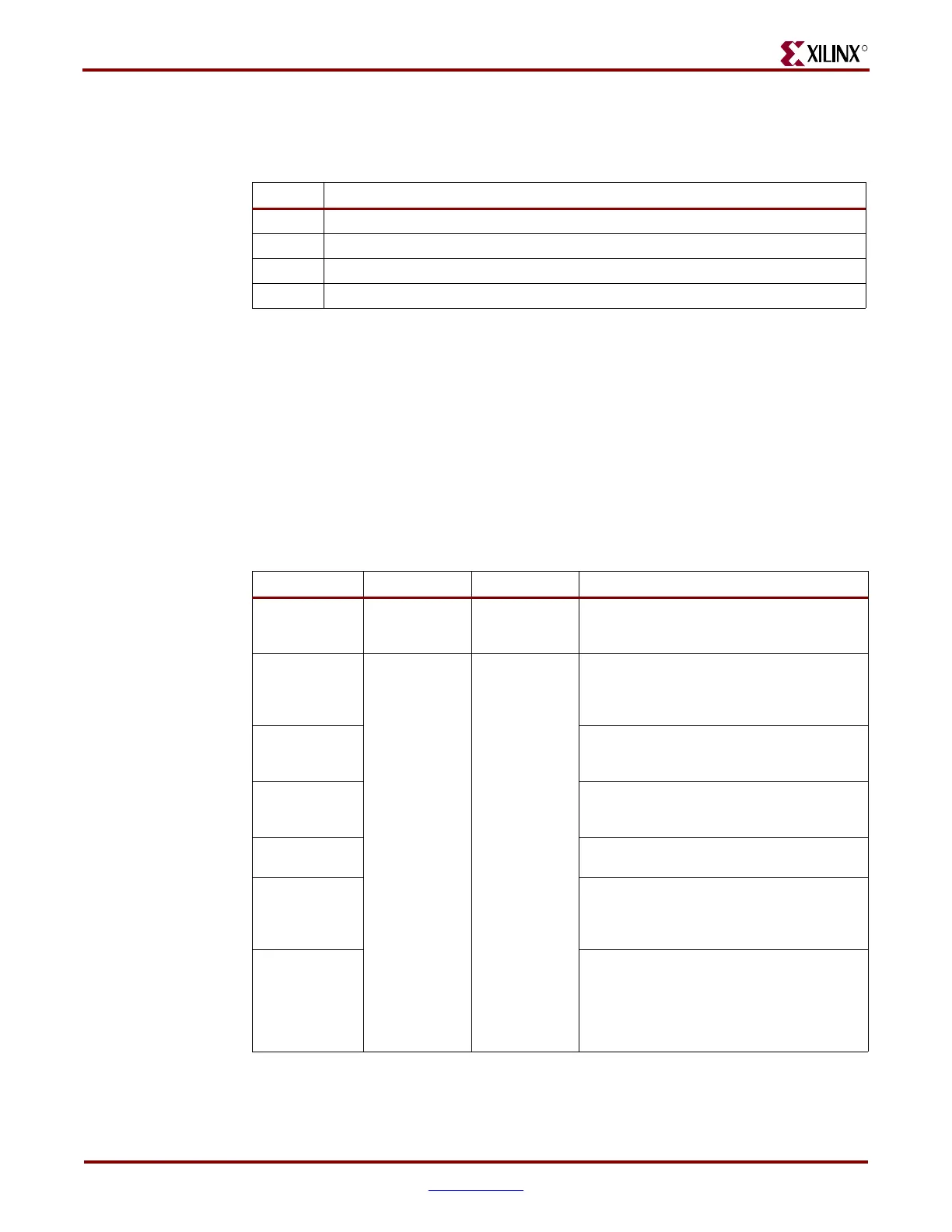

Table 1-9: Default Sequence of Startup Events

Phase Event

4Release DONE pin

5 Negate GTS, activating I/O

6 Assert GWE, allowing RAMs and FFs to change state

7Assert EOS

Table 1-10: Signals Relating to Status Register

Signal Name Type

Access

(1)

Description

DONE Bidirectional

(2)

DONE pin or

Virtex-4 Status

Register

Indicates configuration is complete. Can be

held Low externally to synchronize startup

with other FPGAs.

Release_DONE

Status

Virtex-4

Status

Register

Indicates whether device has released

DONE pin. If pin is held Low externally,

Release_DONE can differ from actual value

on DONE pin.

GWE Global Write Enable. When de asserted GWE

disables CLB and IOB flips-flops as well as

other synchronous elements on the FPGA.

GTS Global Tri-State. When asserted, GTS

disables all the I/O drivers except for

configuration pins.

EOS End of Startup. EOS indicates the absolute

end of the configuration and startup process.

DCI_MATCH DCI_MATCH indicates when all the

Digitally Controlled Impedance (DCI)

controllers have matched their internal

resistor to the external reference resistor.

DCM_LOCK DCM_LOCK indicates when all the Digital

Clock Managers (DCMs) have locked. This

signal is asserted by default. It is active if the

LOCK_WAIT option is used on a DCM and

the LockCycle option is used when the

bitstream is generated.

Notes:

1. Information on the Virtex-4 status register is available in Table 7-9. Information on accessing the JTAG

capture sequence is available in Table 8-4.

2. Open-drain output by default; optional driver enabled using BitGen drivedone option.

Loading...

Loading...