GR740-UM-DS, Nov 2017, Version 1.7 109 www.cobham.com/gaisler

GR740

10.6.2 SDRAM configuration register 2

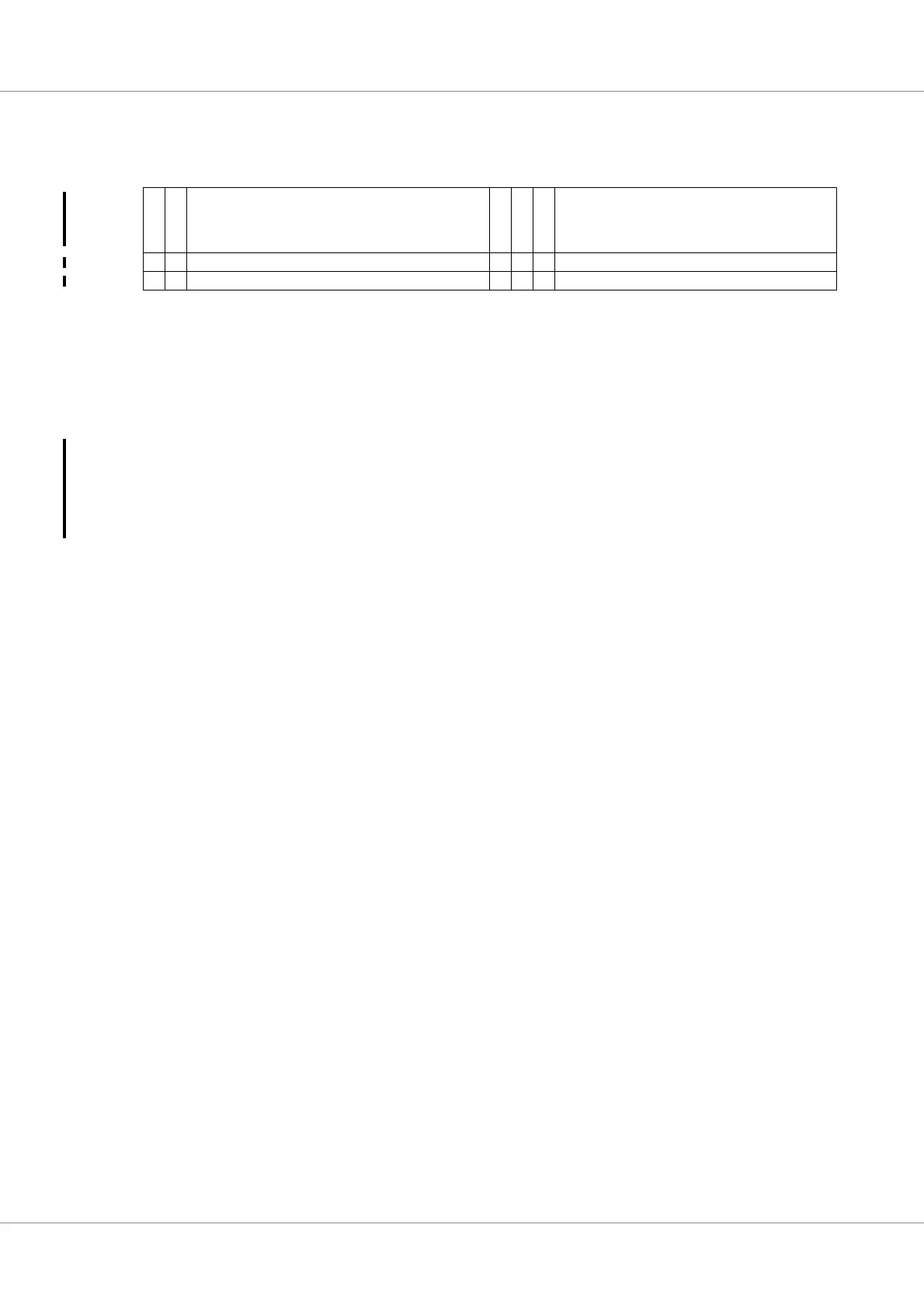

Table 96. 0x04 - SDCFG2 - SDRAM configuration register 2

31 30 29 24 16 15 14 13 12 0

R CE RESERVED E

N

2

T

D

C

S

B

P

A

R

K

RESERVED

0100000

r rw r rw rw rw* r

31 RESERVED

30 Clock enable (CE) - This value is driven on the CKE inputs of the SDRAM. Should be set to ‘1’ for

correct operation.

29: 16 RESERVED

15 Enable 2T signaling (EN2T)

14 Double chip select mode (DCS)

13 Bus parking enable (BPARK) - When this field is set to ’1’ the controller will start to drive the

SDRAM DQ bus eight cycles after the controller has entered idle mode. The value driven is the last

value read from the SDRAM bus. Bus parking is used to guarantee defined levels on the data bus

that would otherwise be left floating and avoids the need of external pull-ups on the data bus.

This functionality is only available in GR740 silicon revision 1. In revision 0 the field is read-only

and tied to ’0’.

12: 0 RESERVED

Loading...

Loading...