GR740-UM-DS, Nov 2017, Version 1.7 128 www.cobham.com/gaisler

GR740

12.5.1 IO Page Table Entry

Address translation is performed by looking up translation information in a one-level table present in

main memory. Part of the incoming address is used to index the table that consists of IO Page Table

Entries. The format of an IO Page Table Entry (IOPTE) is shown in table 124 below.

When the core has IOMMU protection enabled all, incoming accesses from masters belonging to an

active group, which is not in pass-through mode, will be matched against TMASK. If an access is out-

side the range specified by ITR/TMASK, the access will be inhibited and may receive an AMBA

ERROR response (not applicable when the access is a posted write).

If the incoming access is within the range specified by ITR/TMASK, the core will use the incoming

IO address to index the page table containing the address translation information for the master/IO

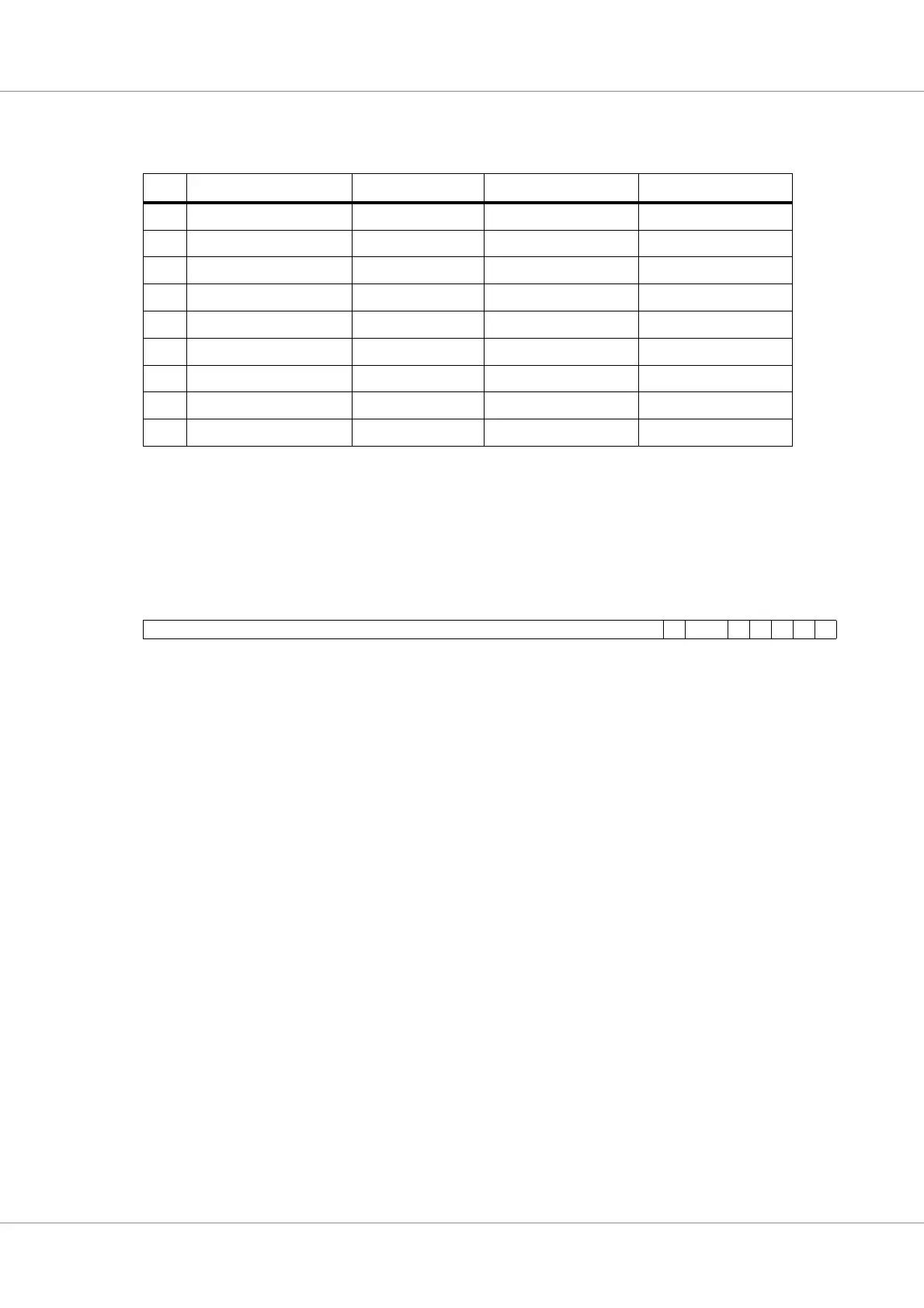

Table 123.Effects of IOMMU Translation Range setting

ITR Size of translated range TMASK bits used Number of pages Size of page tables

0 16 MiB TMASK[31:24]

4096 / 2

pgsz

16 / 2

pgsz

KiB

1 32 MiB TMASK[31:25]

8192 / 2

pgsz

32 / 2

pgsz

KiB

2 64 MiB TMASK[31:26]

16384 / 2

pgsz

64 / 2

pgsz

KiB

3 128 MiB TMASK[31:27]

32768 / 2

pgsz

128 / 2

pgsz

KiB

4 256 MiB TMASK[31:28]

655536 / 2

pgsz

256 / 2

pgsz

KiB

5 512 MiB TMASK[31:29]

131072 / 2

pgsz

512 / 2

pgsz

KiB

6 1024 MiB TMASK[31:30]

262144 / 2

pgsz

1 / 2

pgsz

MiB

7 2048 MiB TMASK[31]

524288 / 2

pgsz

2 / 2

pgsz

MiB

8 4096 MiB TMASK not used

1048576 / 2

pgsz

4 / 2

pgsz

MiB

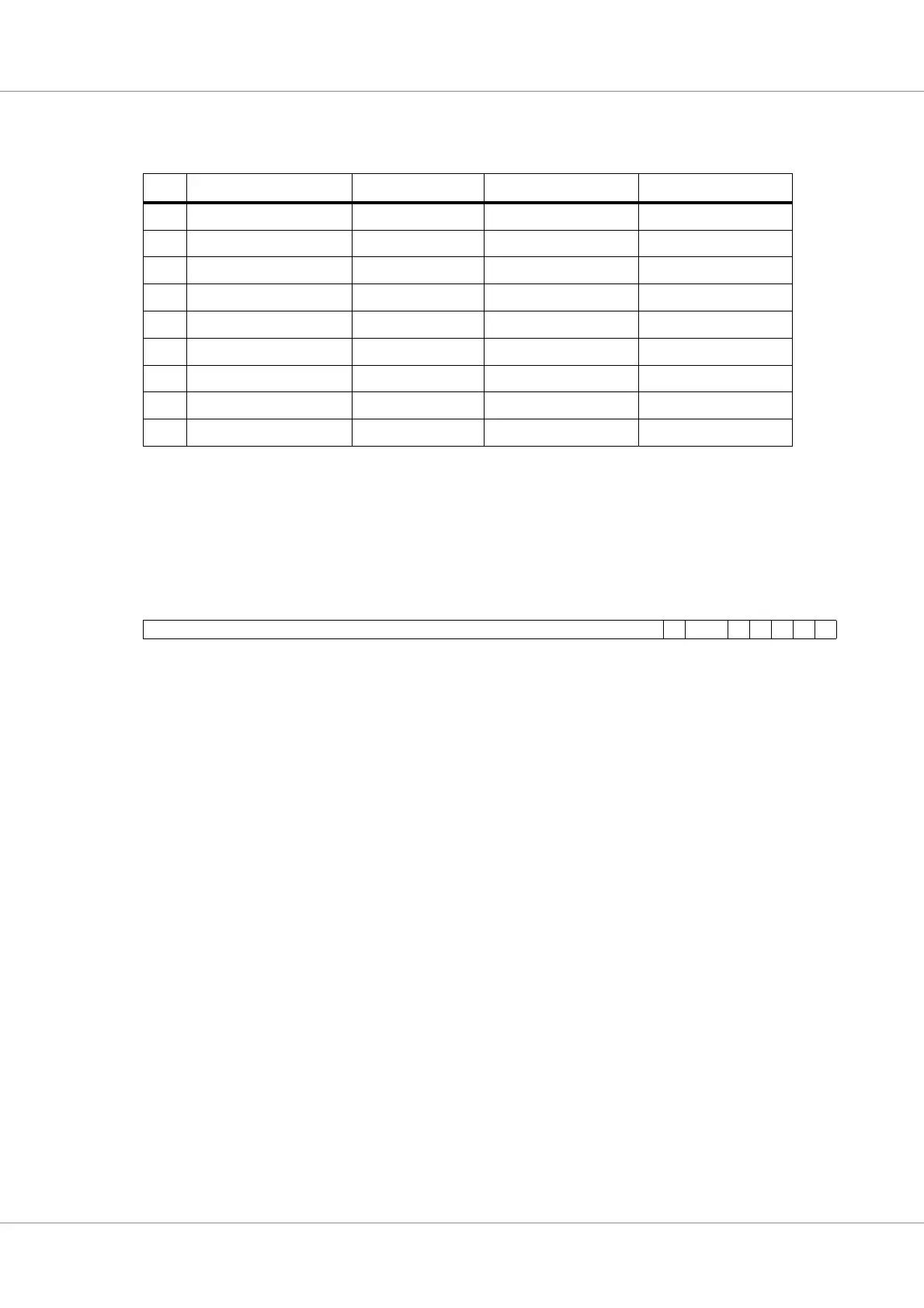

Table 124. IOMMU Page Table Entry (IOPTE)

31 876543210

PPAGE C R BO BS W V R

31:8 Physical Page (PPAGE) - Bits 27:8 of this field corresponds to physical address bits 31:12 of the

page. With a 4 KiB page size, PPAGE[27:8] is concatenated with the incoming IO address bits [11:0]

to form the translated address. For each increase in page size one bit less of PPAGE is used and one

bit more of the incoming IO address is used: this means that with a 16 KiB page size ,

PPAGE[27:10] will be concatenated with the incoming IO address bits [13:0] to form the translated

address.

Bits 31:27 of this field are currently discarded by the IOMMU and are present in the data structure

for forward compatibility with systems using 36-bit AMBA address space.

7 Cacheable (C) - This field is currently not used by the IOMMU

6:5 RESERVED

4 Bus select Override (BO) - If this field is set to ‘1’ then the bus selection is made via the IOPTE.BS

field instead of the per master selection in the Master Configuration register.

3 Bus Select (BS) - Overrides master configuration register BS field when BO field in this IOPTE is

set.

BS = ‘0’ routes traffic over the Processor AHB bus. BS = ‘1’ routes traffic to the Memory AHB bus.

2 Writeable (W) - If this field is ‘1’ write access is allowed to the page. If this field is ‘0’, only read

accesses are allowed.

1 Valid (V) - If this field is ‘1’ the PTE is valid. If this field is ‘0’, accesses to the page covered by this

PTE will be inhibited.

0RESERVED

Loading...

Loading...