GR740-UM-DS, Nov 2017, Version 1.7 294 www.cobham.com/gaisler

GR740

19.9.1 Memory configuration register 1 (MCFG1)

Memory configuration register 1 is used to program the timing of ROM and IO accesses.

During reset, the prom width (bits [9:8]) are set with value on general purpose I/O inputs, see section

3.1. The prom waitstates fields are set to 15 (maximum). External bus ready is disabled. All other

fields are undefined.

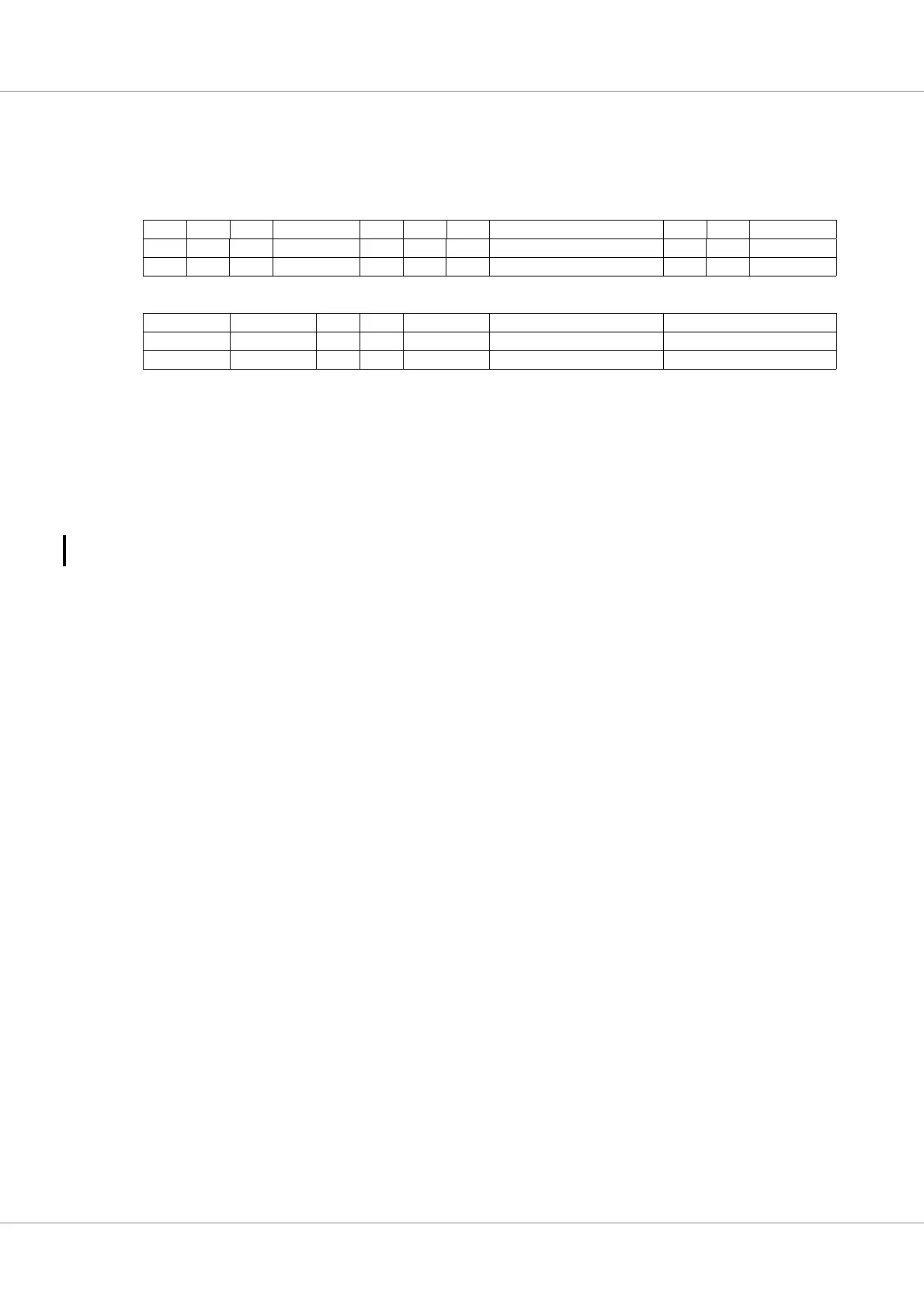

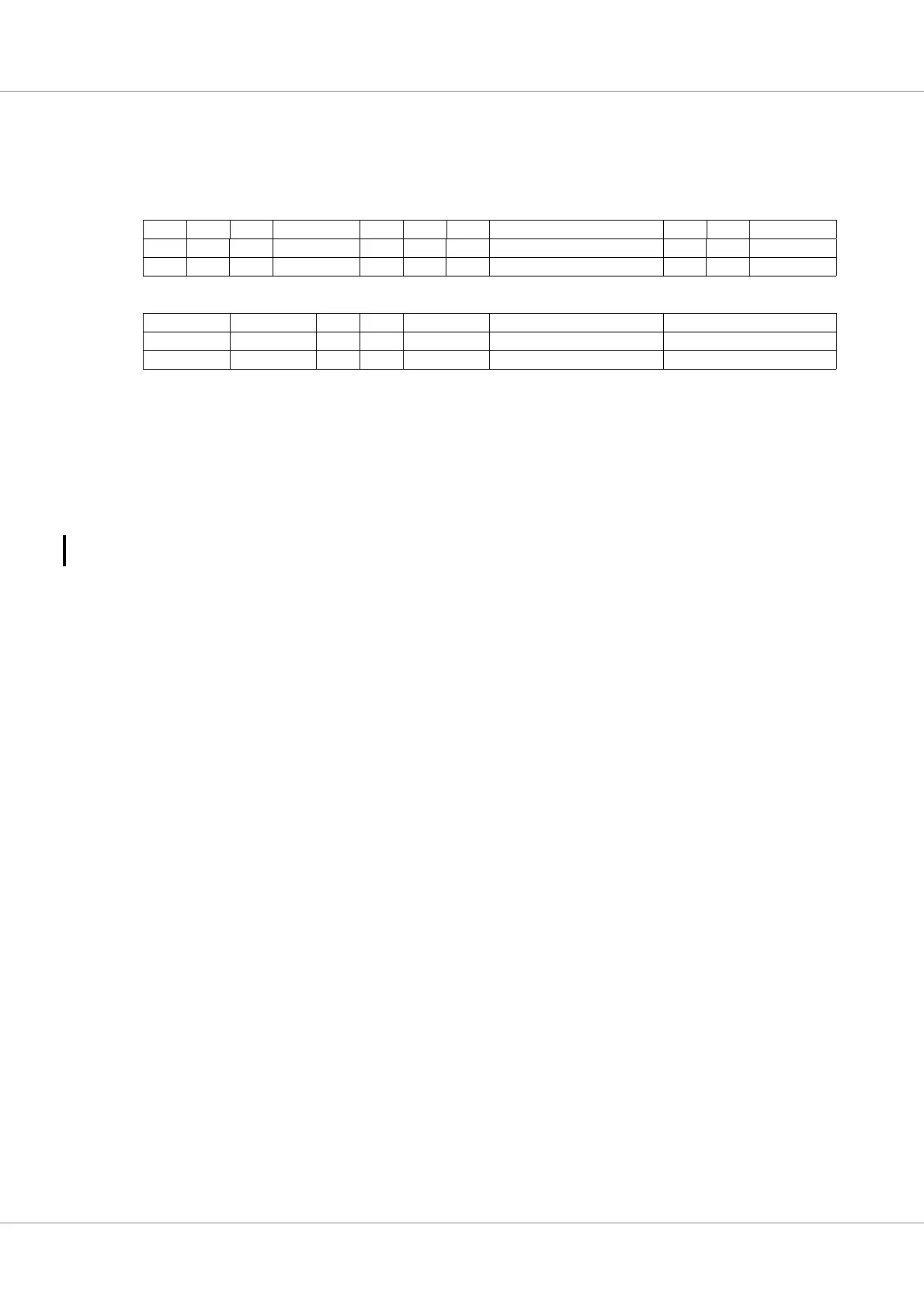

Table 365. Memory configuration register 1

31 30 29 28 27 26 25 24 23 20 19 18 17

PBRDY ABRDY IOBUSW IBRDY BEXCN RES IO WAITSTATES IOEN ROMBANKSZ

00N/R00 0x000x0

rw rw rw rw rw rw rw rw

14 13 12 11 10 9 8 7 4 3 0

RESERVED PWEN PROM WIDTH PROM WRITE WS PROM READ WS

0 (bootstrap) 0xF 0xF

rw rw rw rw rw

31 RESERVED

30 PROM area bus ready enable (PBRDY) - Enables bus ready (BRDYN) signalling for the PROM

area. Reset to ‘0’.

29 Asynchronous bus ready (ABRDY) - Enables asynchronous bus ready.

28 : 27 I/O bus width (IOBUSW) - Sets the data width of the I/O area (“00”=8, “01”=16, others=Illegal).

26 I/O bus ready enable (IBRDY) - Enables bus ready (BRDYN) signalling for the I/O area. Reset to

‘0’.

25 Bus Error Enable (BEXCN) - Generate AMBA error response if external memory bus timeouts. (see

section 5.10 for information on ERROR response propagation)

24 RESERVED

23 : 20 I/O waitstates (IO WAITSTATES) - Sets the number of waitstates during I/O accesses (“0000”=0,

“0001”=8, “0010”=16,..., “1111”=120). The number of waitstates is 8*(IO WAITSTATES).

19 I/O enable (IOEN) - Enables accesses to the memory bus I/O area.

18 RESERVED

17: 14 PROM bank size (ROMBANKSZ) - Returns current PROM bank size when read. “0000” is a spe-

cial case and corresponds to a bank size of 256 MiB. All other values give the bank size in binary

steps: “0001”=16KiB, “0010”=32KiB, ... , “1111”=256 MiB.

Programmable bank sizes can be changed by writing to this register field. The written values corre-

spond to the bank sizes and number of chip-selects as above. Reset to “0000” when programmable.

13:12 RESERVED

11 PROM write enable (PWEN) - Enables write cycles to the PROM area.

10 RESERVED

9 : 8 PROM width (PROM WIDTH) - Sets the data width of the PROM area (“00”=8, “01”=16, oth-

ers=Illegal).

7 : 4 PROM write waitstates (PROM WRITE WS) - Sets the number of wait states for PROM write

cycles (“0000”=0, “0001”=16, “0010”=32,..., “1111”=240). The number of waitstates is 16*(PROM

WRITE WS).

3 : 0 PROM read waitstates (PROM READ WS) - Sets the number of wait states for PROM read cycles

(“0000”=0, “0001”=16, “0010”=32,...,”1111”=240). The number of waitstates is 16*(PROM READ

WS). Reset to “1111”.

Loading...

Loading...