GR740-UM-DS, Nov 2017, Version 1.7 34 www.cobham.com/gaisler

GR740

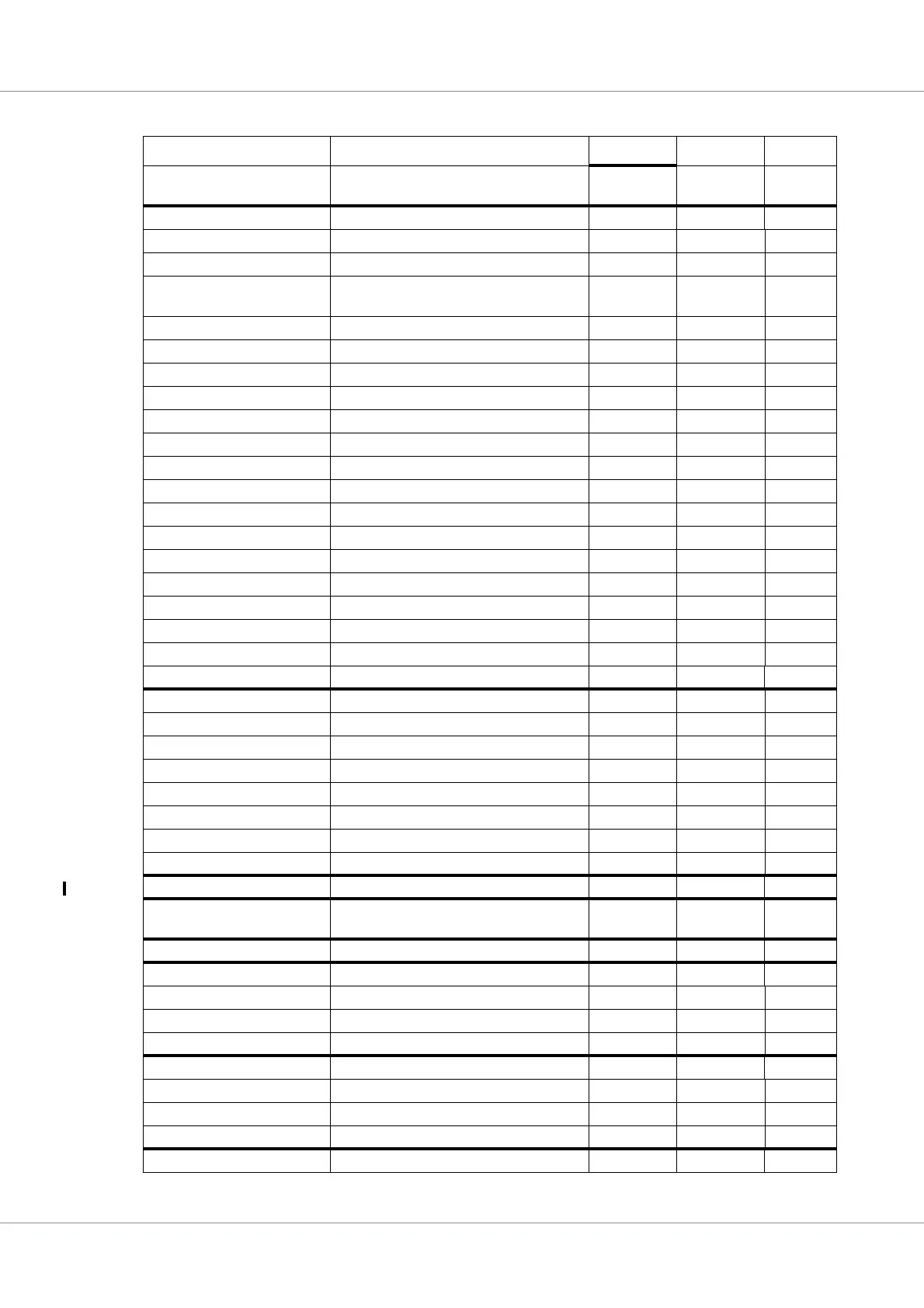

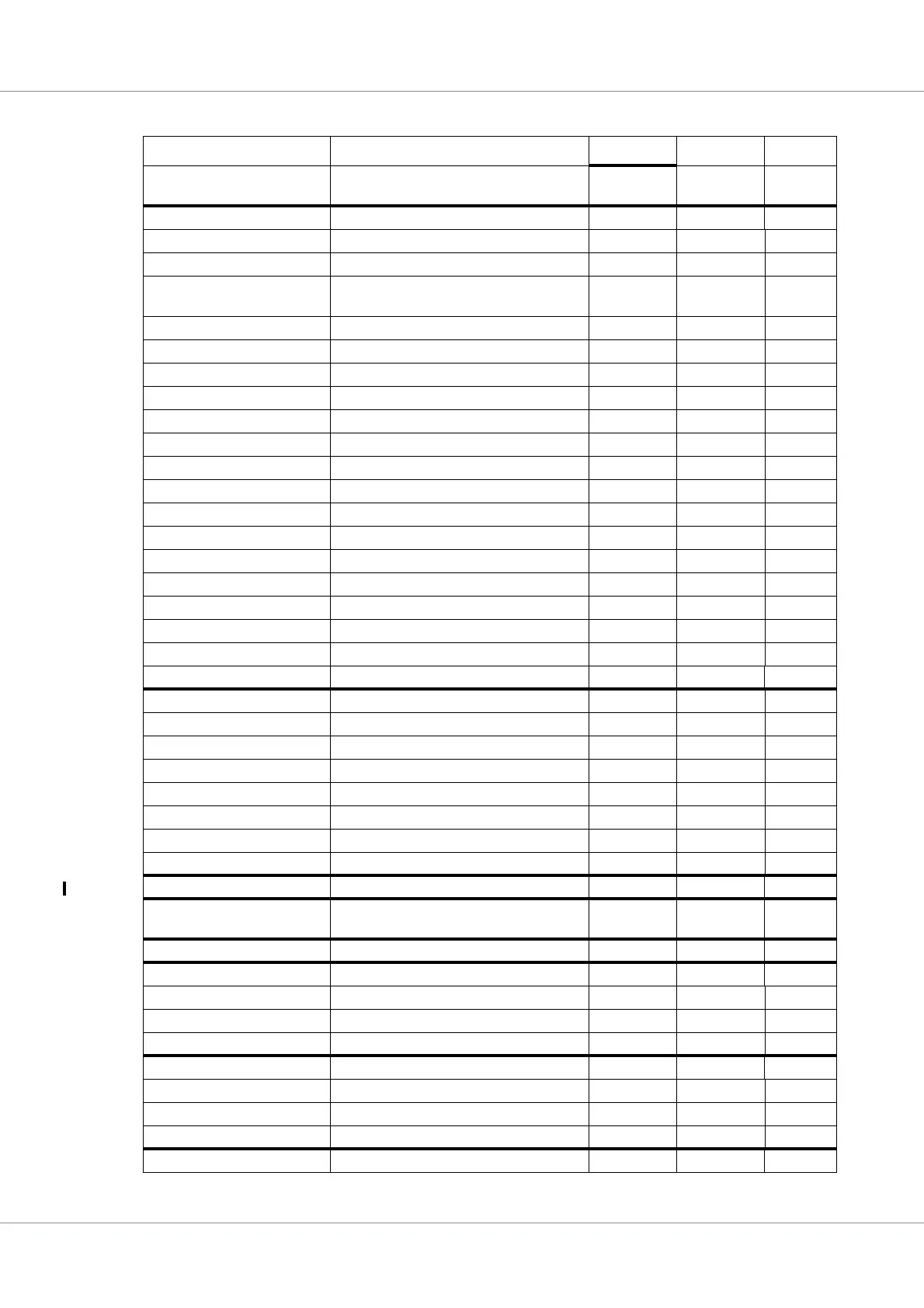

SPW_RXS_N[7:0] SpaceWire router ports 1 - 8, receive strobe,

negative

No In -

PCI_CLK PCI clock See 3.3.2 In -

PCI_GNT PCI grant See 3.3.2 In Low

PCI_IDSEL PCI Device select during configuration See 3.3.2 In High

PCI_HOSTN PCI System host. Low = Device will act as

PCI host

See 3.3.2 In Low

PCI_AD[31:0] PCI Address and Data bus See 3.3.2 BiDir High

PCI_CBE[3:0] PCI Bus command and byte enable See 3.3.2 BiDir Low

PCI_FRAME PCI Cycle frame See 3.3.2 BiDir Low

PCI_IRDY PCI Initiator ready See 3.3.2 BiDir Low

PCI_TRDY PCI Target ready See 3.3.2 BiDir Low

PCI_DEVSEL PCI Device select See 3.3.2 BiDir Low

PCI_STOP PCI Stop See 3.3.2 BiDir Low

PCI_PERR PCI Parity error See 3.3.2 BiDir Low

PCI_SERR PCI System error See 3.3.2 BiDir Low

PCI_PAR PCI Parity signal See 3.3.2 BiDir High

PCI_INTA PCI Interrupt A See 3.3.2 BiDir Low

PCI_INTB PCI Interrupt B See 3.3.2 In Low

PCI_INTC PCI Interrupt C See 3.3.2 In Low

PCI_INTD PCI Interrupt D See 3.3.2 In Low

PCI_REQ PCI Request signal See 3.3.2 Out Low

PCI_M66EN PCI 66 MHz enable signal See 3.3.2 In High

PROM_CEN[1:0] PROM chip select See 3.3.1 Out Low

PROMIO_ADDR[27:0] PROM/IO address See 3.3.1 Out -

PROMIO_OEN PROM/IO Output Enable No Out Low

PROMIO_WEN PROM/IO Write Enable No Out Low

PROMIO_BRDYN PROM/IO Bus ready No In Low

PROMIO_READ PROM/IO Bus reading (for buffer control) No Out High

PROMIO_DATA[15:0] PROM/IO data See 3.3.1 BiDir -

IO_SN PROM/IO chip select See 3.3.1 Out Low

WDOGN Watchdog output No Out-Tri Low

GPIO[15:0] General Purpose I/O See 3.3.1 and

3.1

Bidir -

GPIO2[21:0] Second GPIO See 3.3.1

UART0_TXD UART 0, transmit data See 3.3.1 Out -

UART0_RXD UART 0, receive data See 3.3.1 In -

UART0_RTSN UART 0, request to sent See 3.3.1 Out Low

UART0_CTSN UART 0, clear to send See 3.3.1 In Low

UART1_TXD UART 1, transmit data See 3.3.1 Out -

UART1_RXD UART 1, receive data See 3.3.1 In -

UART1_RTSN UART 1, request to sent See 3.3.1 Out Low

UART1_CTSN UART 1, clear to send See 3.3.1 In Low

GR1553_BUSARXEN MIL-STD-1553 Bus A receiver enable See 3.3.1 Out High

Table 28. All external signals, before pin sharing

Name Usage Pin sharing Direction Polarity

Loading...

Loading...