GR740-UM-DS, Nov 2017, Version 1.7 30 www.cobham.com/gaisler

GR740

3.3.2 SDRAM interface multiplexing

The top half of the SDRAM interface shares pins with PCI and Ethernet port 1. The selection between

full SDRAM, PCI and Ethernet is made with the bootstrap signals MEM_IFWIDTH and PCI-

MODE_ENABLE.

This configuration is static and should be kept constant during the runtime

of the device (a change will require a full reset of the device). Some of the data mask (DQM)

bits are used as clock inputs in the alternative modes, and their direction will therefore depend on con-

figuration.

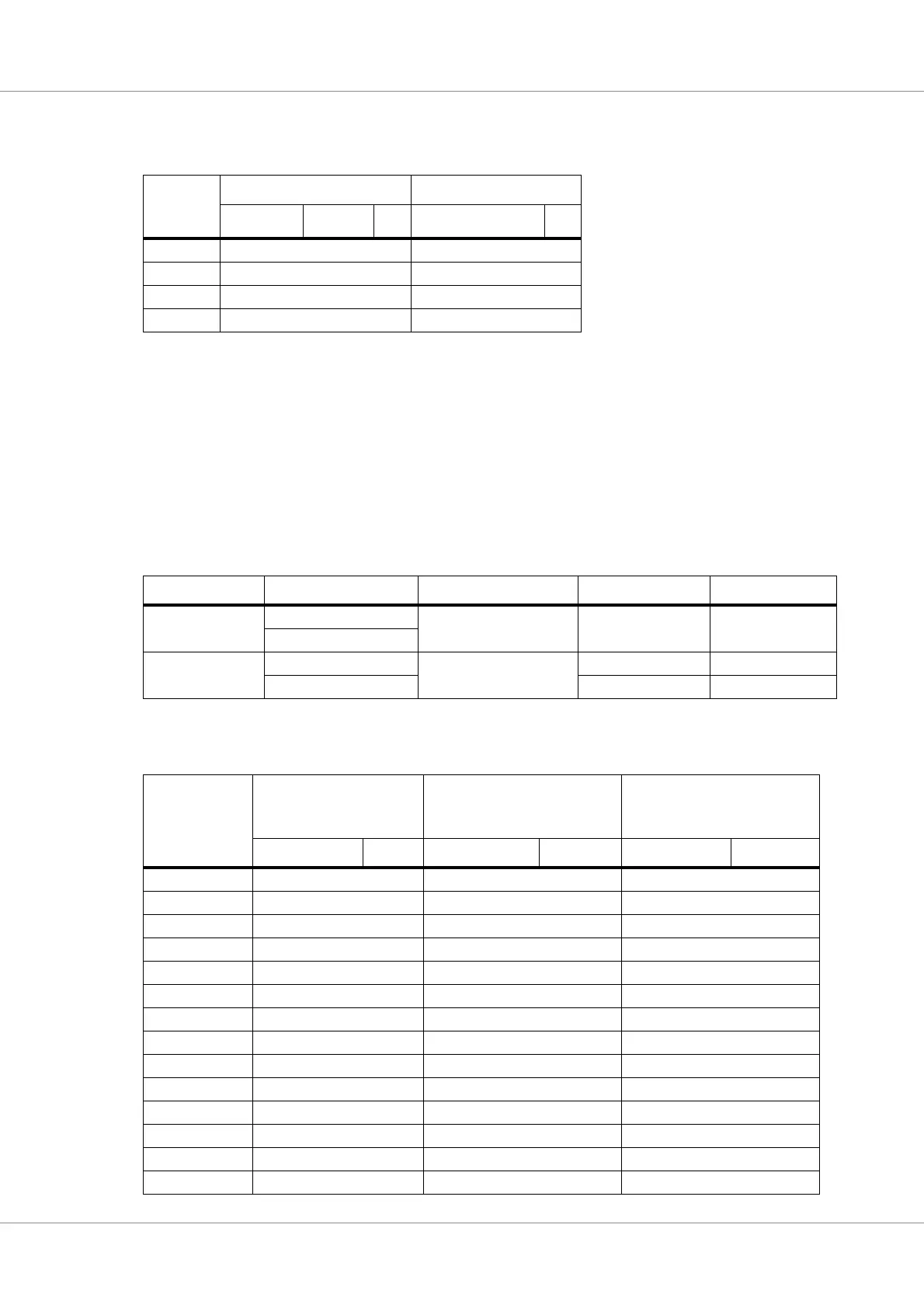

Table 25. Shared GPIO interface pins with slow interfaces

Pin name* Primary function Second function

Signal Dir Signal Dir

GPIO[7] (as pin name) IO SPWD_RXD I

GPIO[6] (as pin name) IO SPWD_RXS I

GPIO[5] (as pin name) IO UART0_CTSN I

GPIO[4] (as pin name) IO UART1_CTSN I

* See section 40.3 for pin assignments

Table 26. Selection between SDRAM, PCI and Ethernet 1

MEM_IFWIDTH PCIMODE_ENABLE SDRAM interface Ethernet port 1 PCI

0 0 64 data bits, 32 check bits Unavailable Unavailable

1

1 0 32 data bits, 16 check bits Available Unavailable

1 Unavailable Available

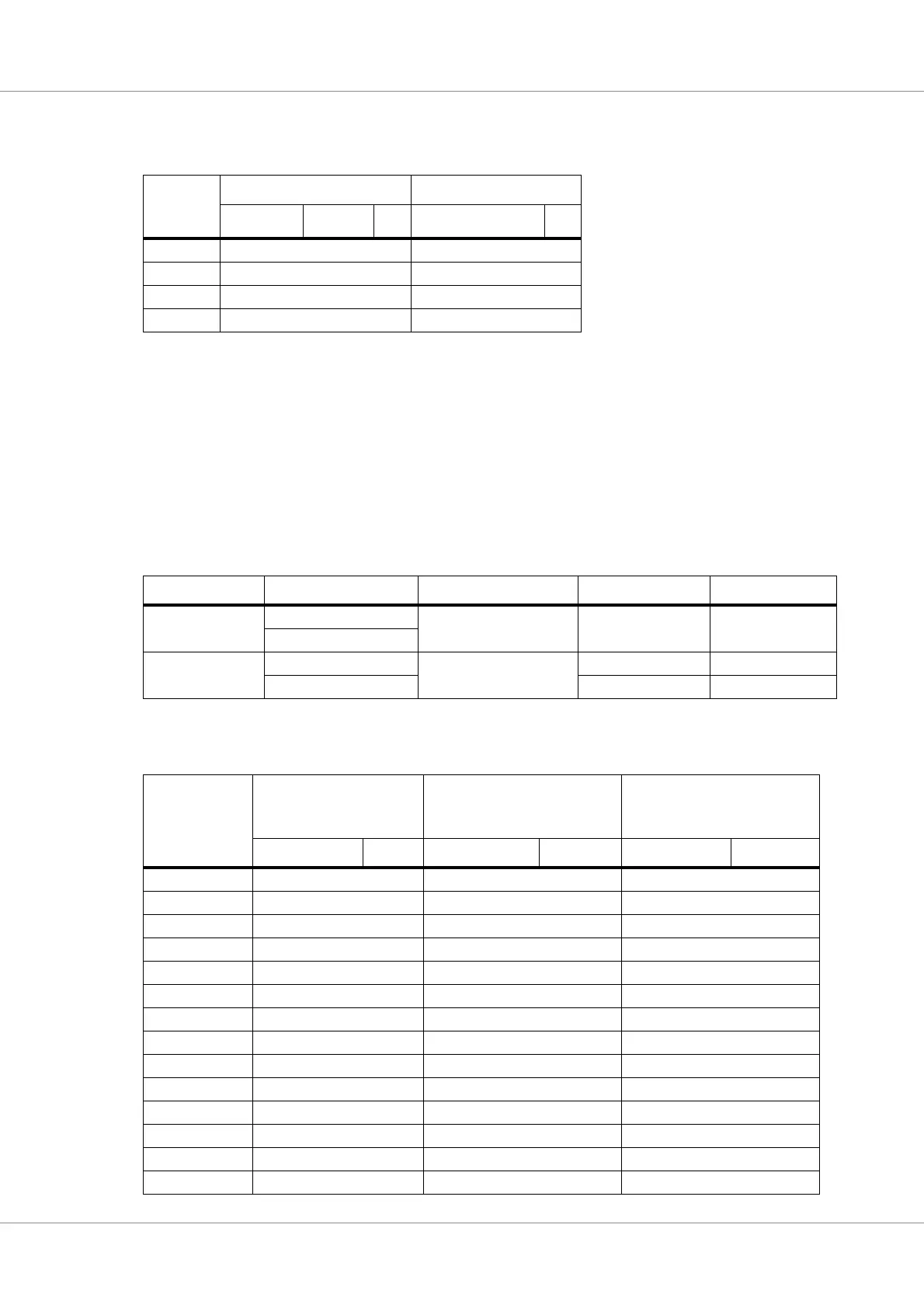

Table 27. Multiplexed SDRAM interface pins with PCI or Ethernet interfaces

Pin name*

SDRAM function

(MEM_IFWIDTH=LOW)

ETHERNET1 function

(MEM_IFWIDTH=HIGH,

PCIMODE_ENABLE=LOW)

PCI function

(MEM_IFWIDTH=HIGH,

PCIMODE_ENABLE=HIGH)

Signal Dir Signal Dir Signal Dir

MEM_DQ[95] (as pin name) IO ETH1_TXD[7] O PCI_AD[31] IO

MEM_DQ[94] (as pin name) IO ETH1_TXD[6] O PCI_AD[30] IO

MEM_DQ[93] (as pin name) IO ETH1_TXD[5] O PCI_AD[29] IO

MEM_DQ[92] (as pin name) IO ETH1_TXD[4] O PCI_AD[28] IO

MEM_DQ[91] (as pin name) IO ETH1_TXD[3] O PCI_AD[27] IO

MEM_DQ[90] (as pin name) IO ETH1_TXD[2] O PCI_AD[26] IO

MEM_DQ[89] (as pin name) IO ETH1_TXD[1] O PCI_AD[25] IO

MEM_DQ[88] (as pin name) IO ETH1_TXD[0] O PCI_AD[24] IO

MEM_DQ[87] (as pin name) IO ETH1_TXEN O PCI_AD[23] IO

MEM_DQ[86] (as pin name) IO ETH1_TXER O PCI_AD[22] IO

MEM_DQ[85] (as pin name) IO (none) I PCI_AD[21] IO

MEM_DQ[84] (as pin name) IO (none) I PCI_AD[20] IO

MEM_DQ[83] (as pin name) IO (none) I PCI_AD[19] IO

MEM_DQ[82] (as pin name) IO (none) I PCI_AD[18] IO

Loading...

Loading...