GR740-UM-DS, Nov 2017, Version 1.7 401 www.cobham.com/gaisler

GR740

33.6.12 Instruction count register

The DSU contains an instruction count register to allow profiling of application, or generation of

debug mode after a certain clocks or instructions. The instruction count register consists of a 29-bit

down-counter, which is decremented on either each clock (IC=0) or on each executed instruction

(IC=1). In profiling mode (PE=1), the counter will set to all ones after an underflow without generat-

ing a processor break. In this mode, the counter can be periodically polled and statistics can be formed

on CPI (clocks per instructions). In non-profiling mode (PE=0), the processor will be put in debug

mode when the counter underflows. This allows a debug tool such as GRMON to execute a defined

number of instructions, or for a defined number of clocks.

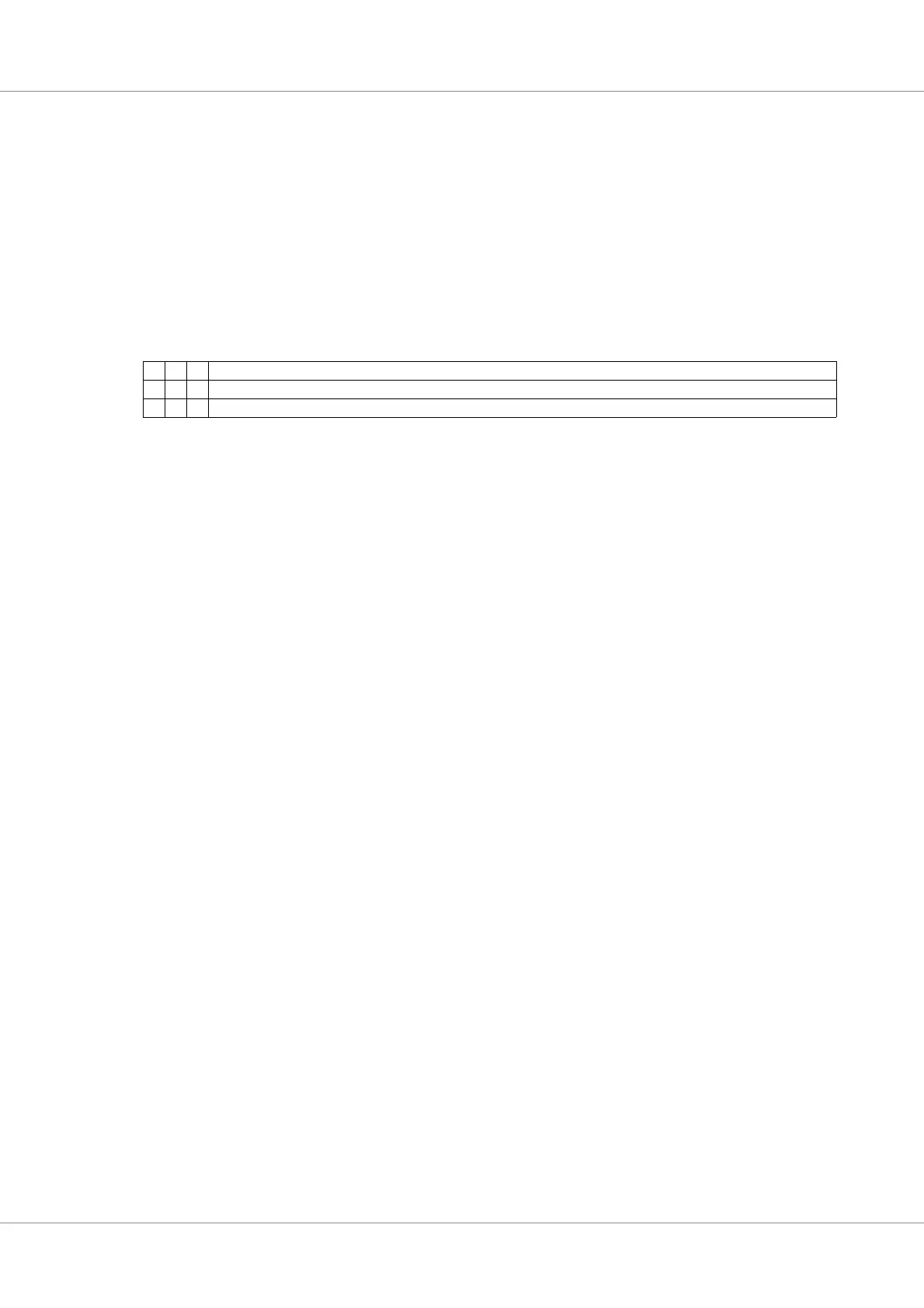

Table 536. 0x000070 - ICNT - Instruction trace count register

31 30 29 28 0

CE IC PE ICOUNT[28:0]

000 NR

rw rw rw rw

31 Counter Enable (CE) - Counter enable

30 Instruction Count (IC) - Instruction (1) or clock (0) counting

29 Profiling Enable (PE) - Profiling enable

28: 0 Instruction count (ICOUNT) - Instruction count

Loading...

Loading...