GR740-UM-DS, Nov 2017, Version 1.7 52 www.cobham.com/gaisler

GR740

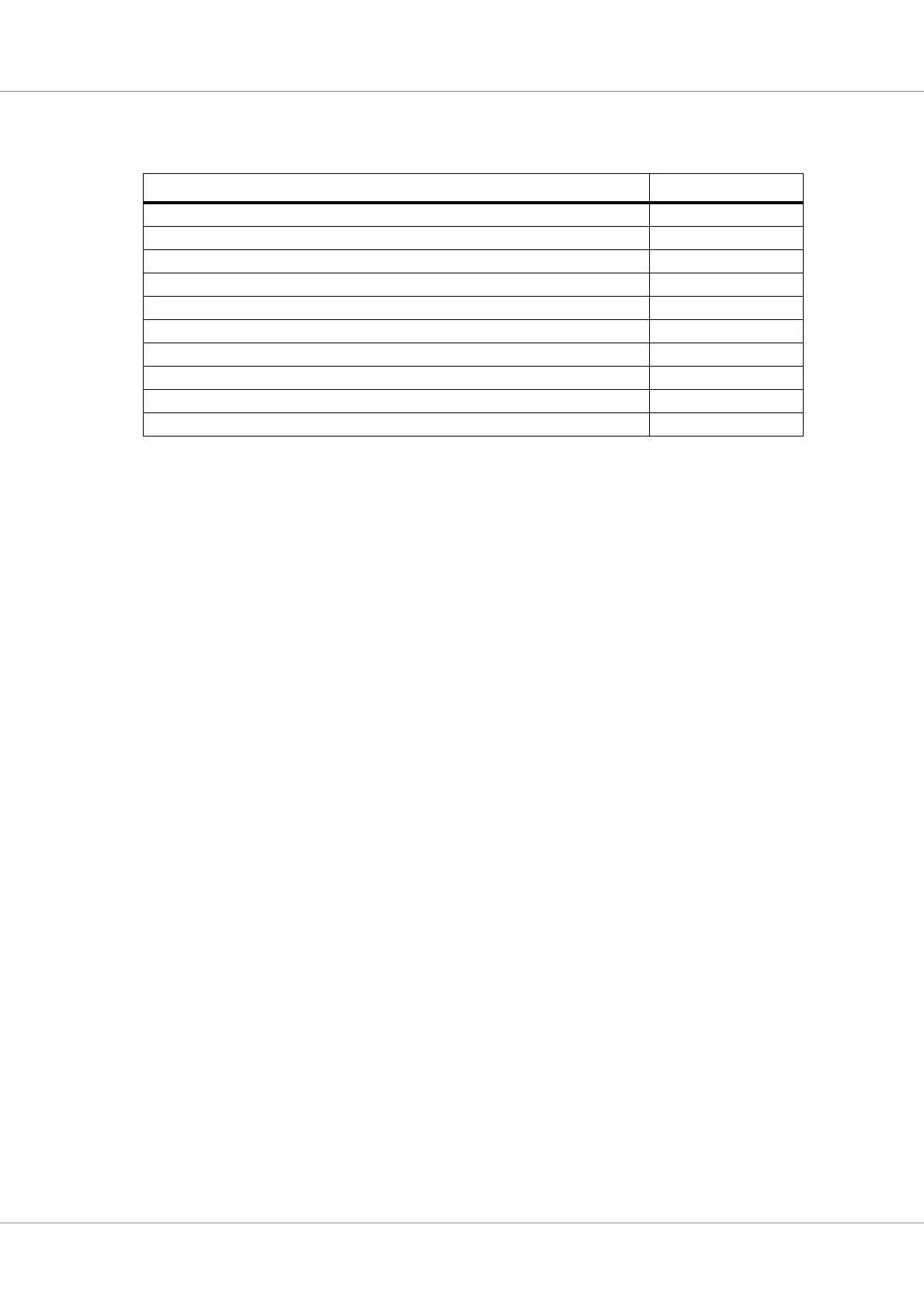

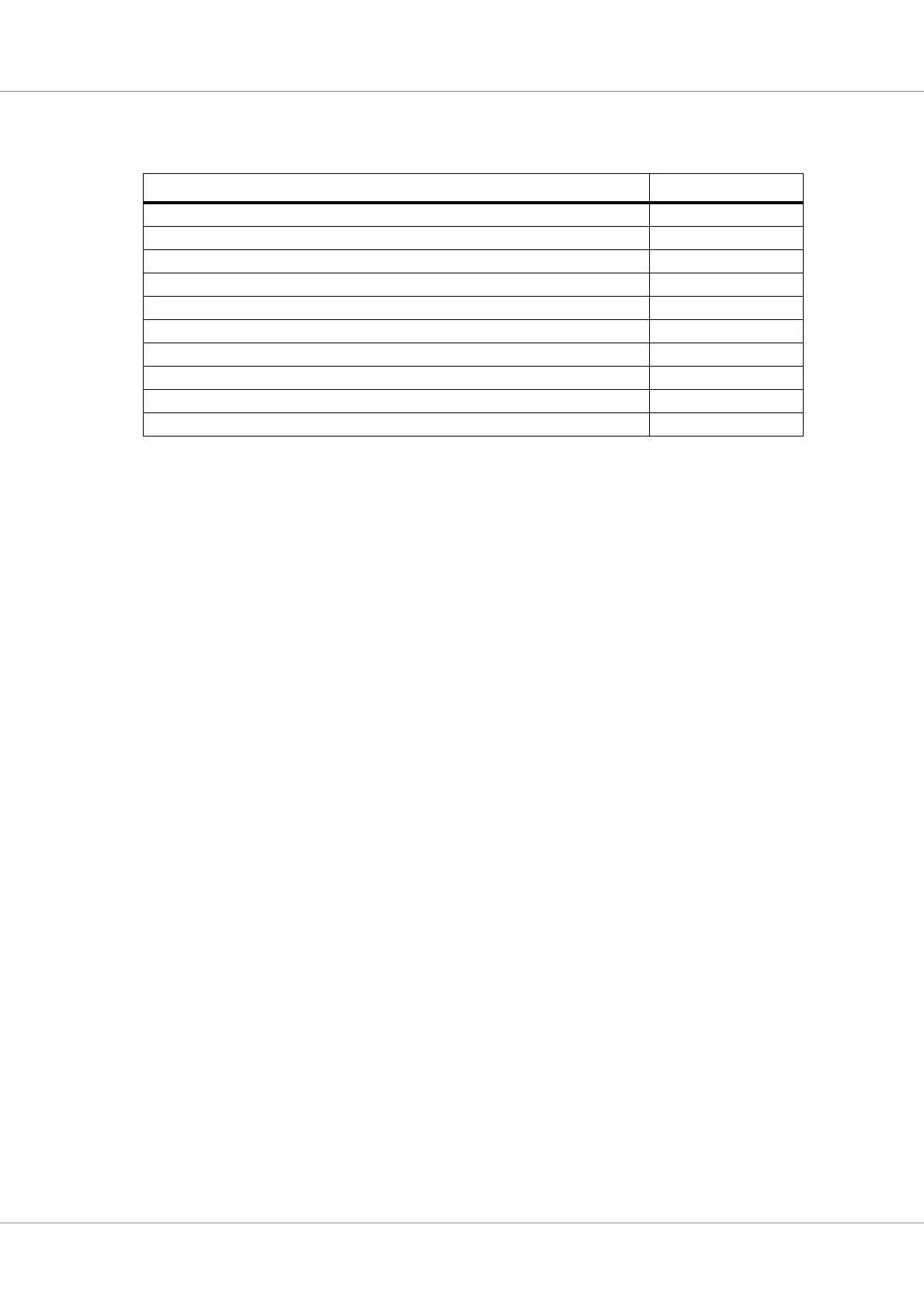

Certain specific events that cause these types of locks and their timing are listed in table 36 below.

6.2.3 SPARC Implementor’s ID

Cobham Gaisler is assigned number 15 (0xF) as SPARC implementor’s identification. This value is

hard-coded into bits 31:28 in the %psr register. The version number for LEON4 is 3 (same as for

LEON3 to provide software compatibility), which is hard-coded in to bits 27:24 of the %psr.

6.2.4 Divide instructions

Full support for SPARC V8 divide instructions is provided (SDIV, UDIV, SDIVCC & UDIVCC). The

divide instructions perform a 64-by-32 bit divide and produce a 32-bit result. Rounding and overflow

detection is performed as defined in the SPARC V8 manual.

6.2.5 Multiply instructions

The LEON processor supports the SPARC integer multiply instructions UMUL, SMUL UMULCC

and SMULCC. These instructions perform a 32x32-bit integer multiply, producing a 64-bit result.

SMUL and SMULCC performs signed multiply while UMUL and UMULCC performs unsigned

multiply. UMULCC and SMULCC also set the condition codes to reflect the result. The multiply

instructions are performed using a 32x32 pipelined hardware multiplier.

6.2.6 Multiply and accumulate instructions

This implementation does not support multiply-and-accumulate (UMAC; SMAC) instructions.

6.2.7 Compare and Swap instruction (CASA)

LEON4 implements the SPARC V9 Compare and Swap Alternative (CASA) instruction. The CASA

operates as described in the SPARC V9 manual. The instruction is privileged, except when setting

ASI = 0xA (user data).

Table 36. Event timing

Event Cycles

Instruction cache miss processing, MMU disabled 3 + mem latency

Instruction cache miss processing, MMU enabled 5 + mem latency

Data cache miss processing, MMU disabled (read), L2 hit 3 + mem latency

Data cache miss processing, MMU disabled (write), write-buffer empty 0

Data cache miss processing, MMU enabled (read) 5 + mem latency

Data cache miss processing, MMU enabled (write), write-buffer empty 0

MMU page table walk 10 + 3 * mem latency

Branch prediction miss, branch follows ICC setting 2

Branch prediction miss, one instruction between branch and ICC setting 1

Pipeline restart due to register file or cache error correction 7

Loading...

Loading...