GR740-UM-DS, Nov 2017, Version 1.7 71 www.cobham.com/gaisler

GR740

6.10.3 ASR17, LEON4 configuration register

The ancillary state register 17 (%asr17) provides information on how the LEON4 implementation has

been configured. This can be used to enhance the performance of software, or to support enumeration

in multi-processor systems. There are also a few bits that are writable to configure certain aspects of

the processor.

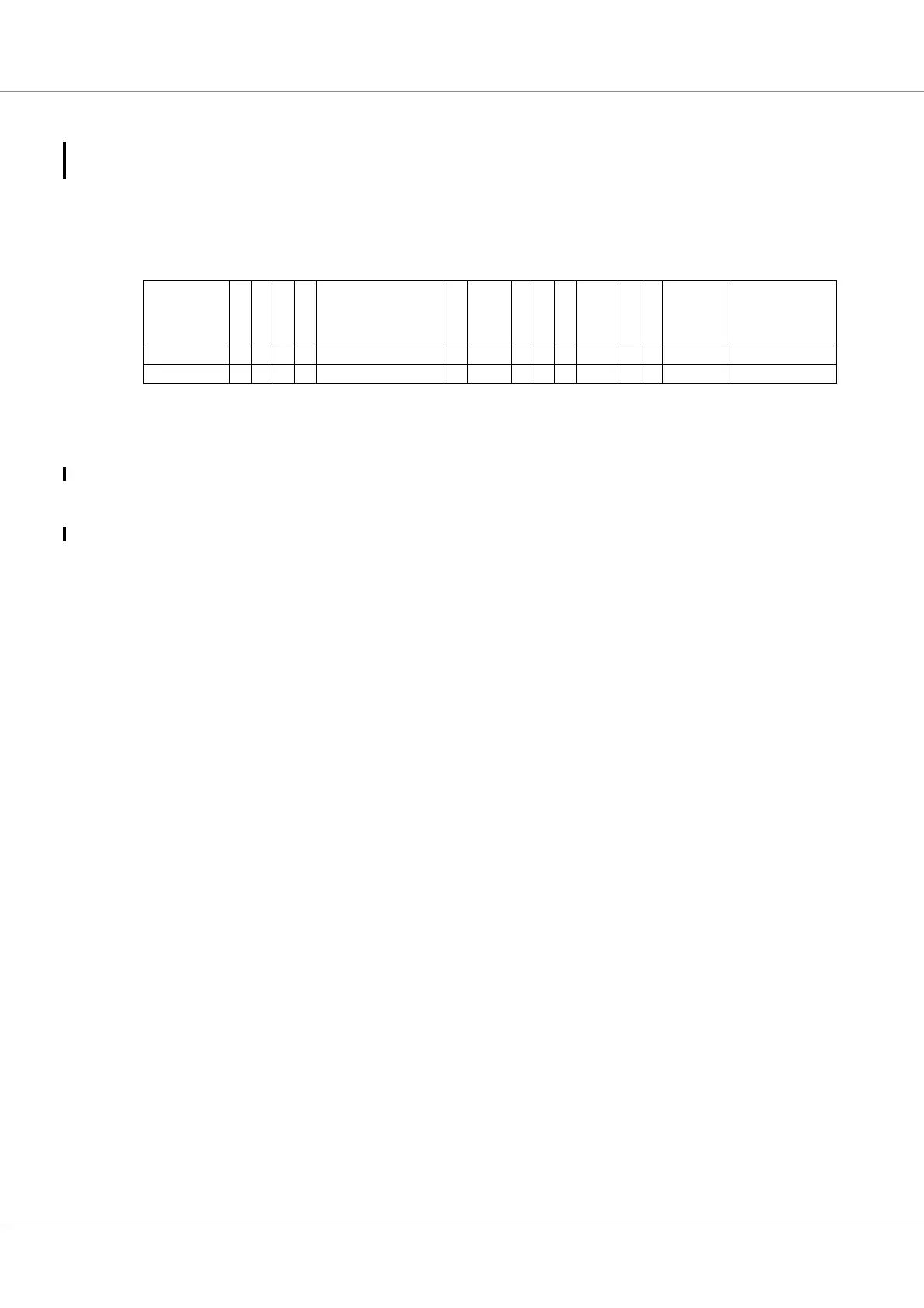

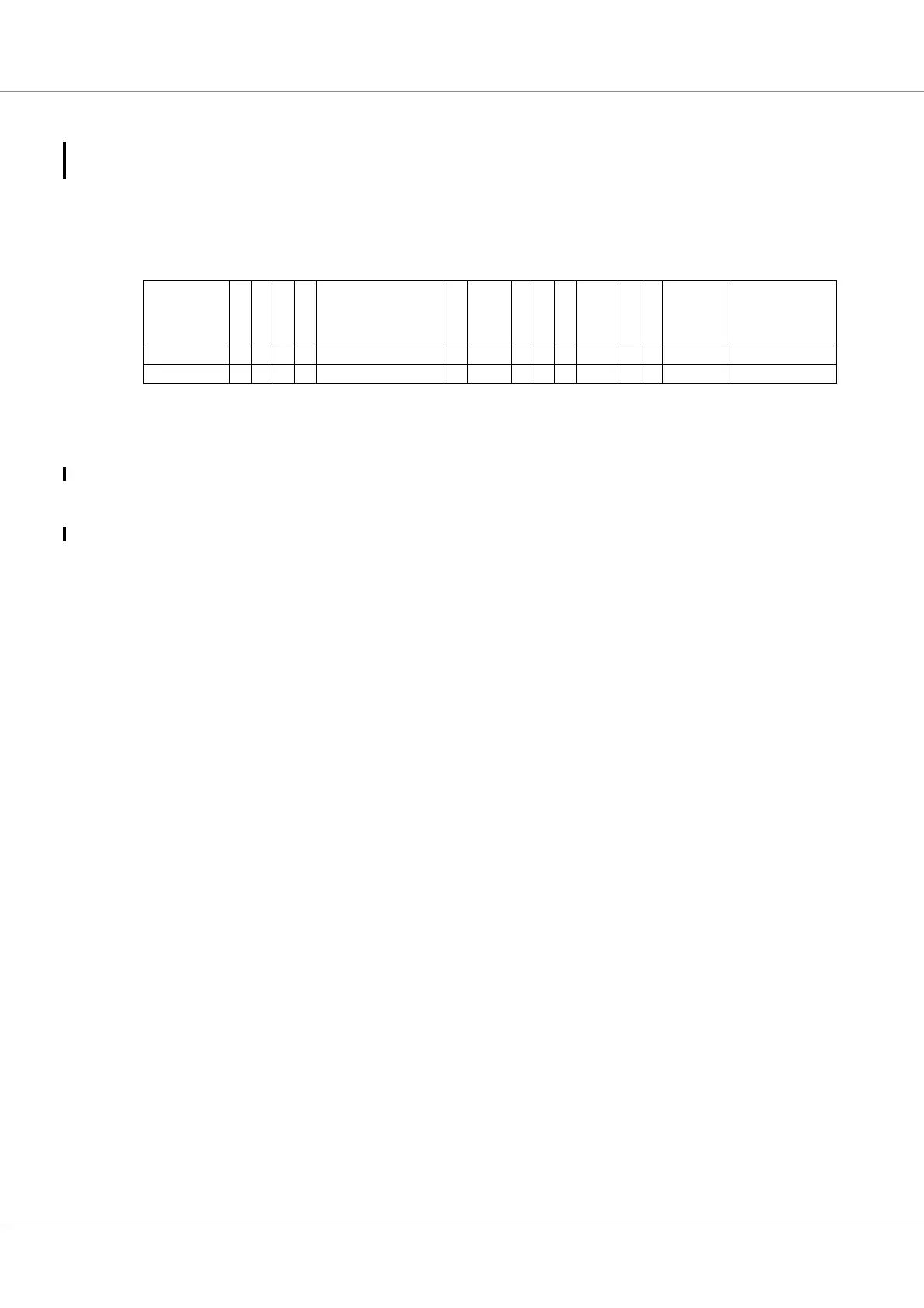

Table 50. %asr17 - LEON4 configuration register

31 28 27 26 25 24 23 18 17 16 15 14 13 12 11 10 8 7 6 5 4 0

INDEX D

B

P

R1 D

B

P

M

R2 RESERVED CS CF DW SV LD FPU M V8 NWP NWIN

0 - 3 0 0 1 0 0 0b00 0 0 0 0b01 0 1 0b100 0x7

r rwrwrwrw r r rwrw r r r r r r

31: 28 Processor index (INDEX) - Each LEON core gets a unique index to support enumeration. The pro-

cessors are numbered 0 - 3.

27 Disable Branch Prediction (DBP) - Disables branch prediction when set to ‘1’.

26 Reserved field (R1) - This field must always be written with ’0’.

25 Disable Branch Prediction on instruction cache misses (DBPM) - When set to ‘1’ this avoids instruc-

tion cache fetches (and possible MMU table walk) for predicted instructions that may be annullated.

24 Reserved field (R2) - This field must always be written with ’0’.

23: 18 Reserved for future implementations

17 Clock switching (CS) - This field is 0 to signify that this implementation does not support clock

switching.

16: 15 CPU clock frequency (CF) - This field is 0 to signify that the CPU runs at the same frequency as the

AMBA bus.

14 Disable write error trap (DWT) - When set, a write error trap (tt = 0x2b) will be ignored. Set to zero

after reset.

13 Single-vector trapping (SVT) enable - If set, will enable single-vector trapping.

12 Load delay (LD) - 0 to signify that a 1-cycle load delay i s used.

11: 10 FPU option (FPU) - "01” = GRFPU.

9 Multiply and accumulate (M) - 0 to signify that (MAC) instructions are unsupported.

8 SPARC V8 (V8) - Set to 1, to signify that the SPARC V8 multiply and divide instructions are avail-

able.

7: 5 Number of implemented watchpoints (NWP) - Value is 4.

4: 0 Number of register windows (NWIN) - Number of implemented registers windows corresponds to

NWIN+1. Field has value 7.

Loading...

Loading...