GR740-UM-DS, Nov 2017, Version 1.7 77 www.cobham.com/gaisler

GR740

6.10.9 MMU context pointer and context registers

The MMU context pointer register is located in ASI 0x19 offset 0x100 and the MMU context register

is located in ASI 0x19 offset 0x200. They together determine the location of the root page table

descriptor for the current context. Their definition follow the SRMMU specification in the SPARC V8

manual with layouts shown below.

In the LEON4, the context bits are OR:ed with the lower MMU context pointer bits when calculating

the address, so one can use less context bits to reduce the size/alignment requirements for the context

table.

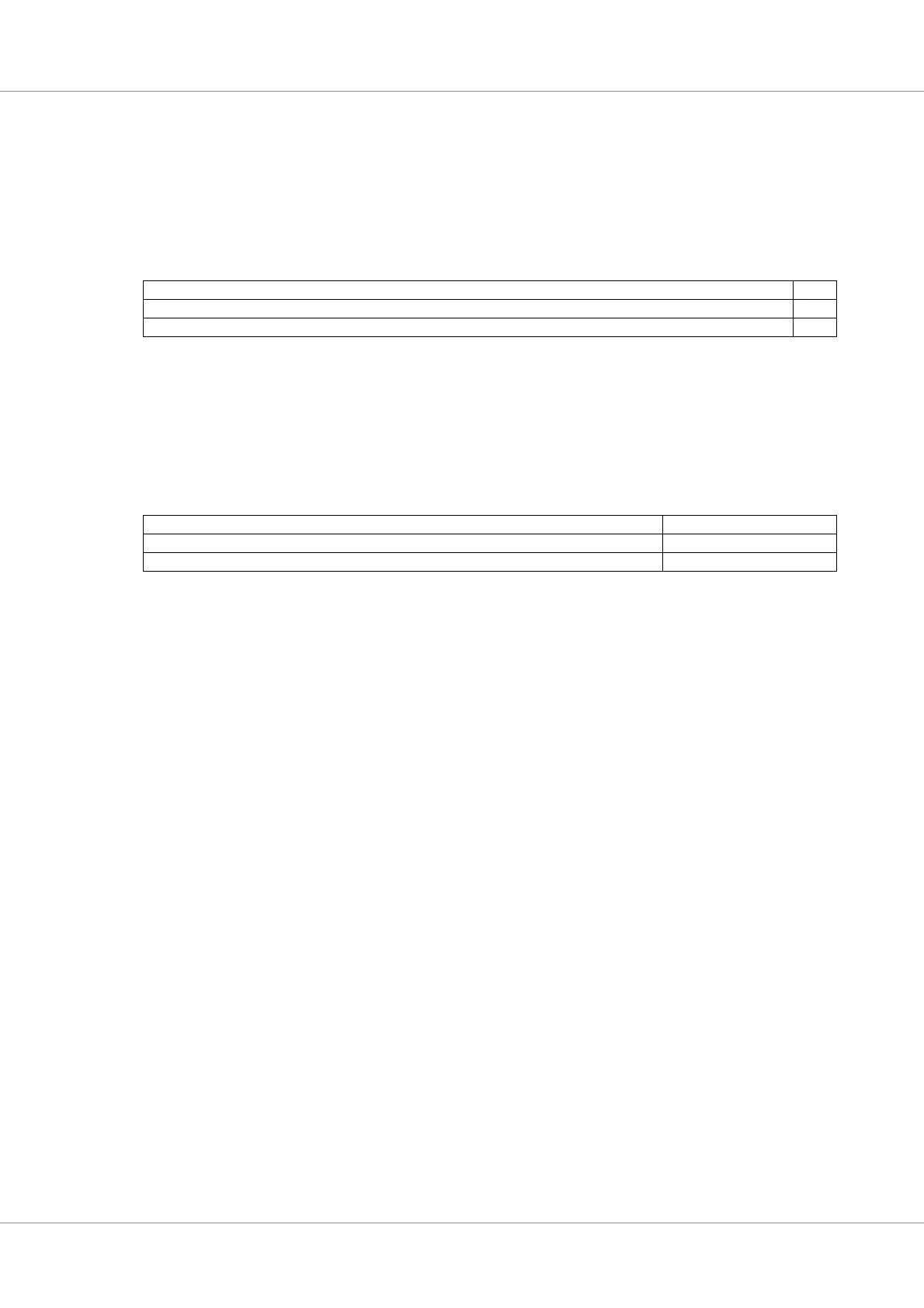

Table 58. ASI 0x19, offset 0x100 - MMUCTXP - MMU context pointer register

31 210

CONTEXT TABLE POINTER R

NR 0

rw rr

31: 2 Context Table Pointer (CONTEXT TABLE POINTER) - Context table pointer, physical address bits

35:6 (note address is shifted 4 bits)

1: 0 Reserved

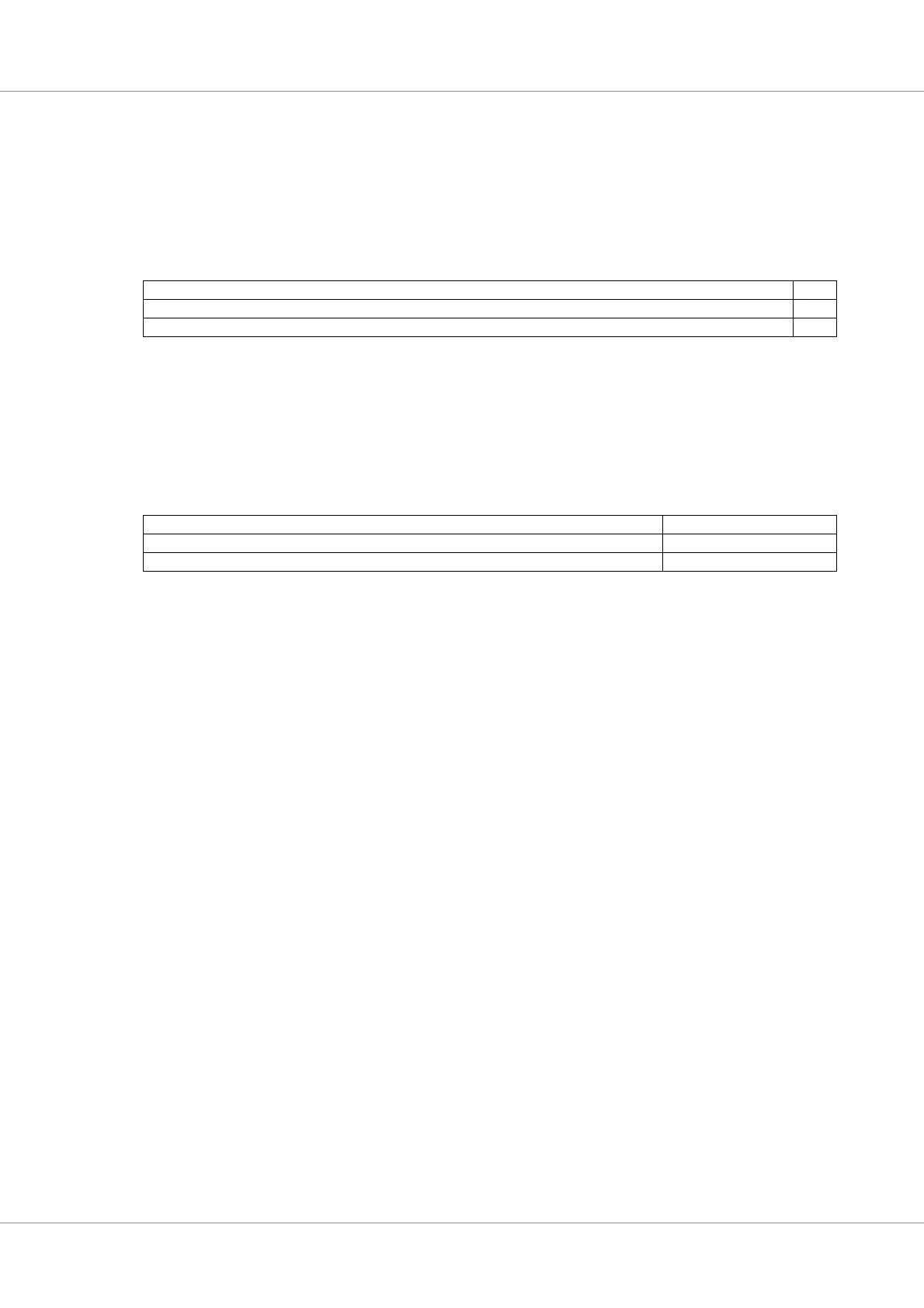

Table 59. ASI 0x19, offset 0x200 - MMUCTX - MMU context register

31 87 0

RESERVED CONTEXT

0 0x00

rrw

31: 8 RESERVED

7: 0 Current contect ID (CONTEXT)

Loading...

Loading...