Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

6-44

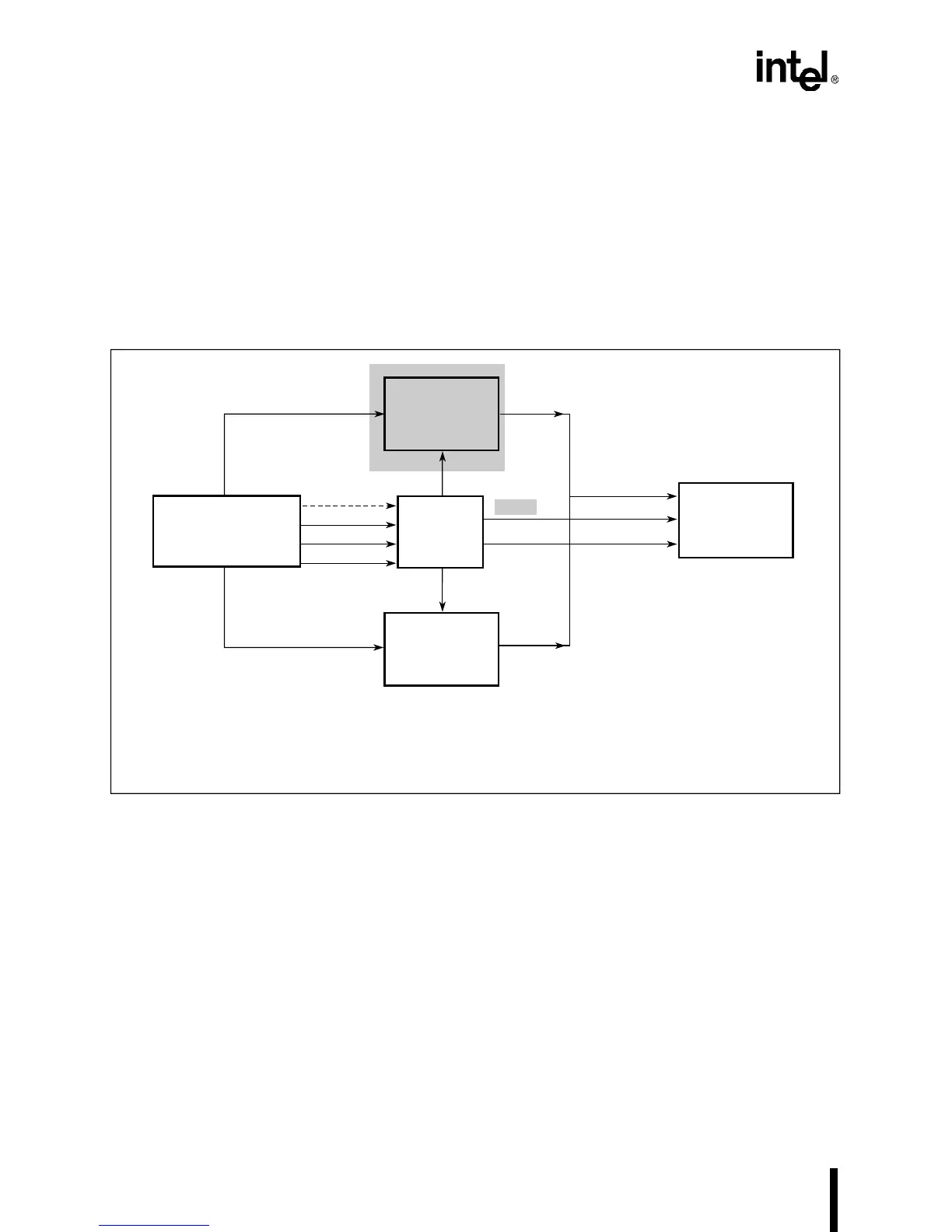

6.6.5 Non-Paged DRAM Interface

This interface is similar to the Paged DRAM Interface, except that in this case, the lower address

bits are routed to the Row Address Buffer and the higher address bits to the Column Address

Buffer. This is done to simplify the RAS#-Only Refresh logic. The PLD in this case enables the

Row Address Buffer and asserts the RAS# signal (shaded sections in the figure) during a Refresh

Cycle. Refer to Chapter 15, “REFRESH CONTROL UNIT,” for more information.

A single multiplexer can be used instead of the separate row and column address buffers.

Figure 6-19. Intel386 EX Processor and Non-Paged DRAM Interface

Intel386™ EX

Embedded Processor

Row

Address

Buffer

PLD

Lower Address

Row

Address

Non-paged

DRAM

Column

Address

Address

Upper Address

OE_ROW#

OE_COL#

RAS#

CAS#

BHE#

BLE#

A3265-02

Column

Address

Buffer

CS

n

#

REFRESH#

Note:

A single mux can be used in place of the row and column address buffers.

Loading...

Loading...