13-5

SYNCHRONOUS SERIAL I/O UNIT

13.2 SSIO OPERATION

The following sections describe the operation of the baud-rate generator, transmitter, and receiv-

er.

13.2.1 Baud-rate Generator

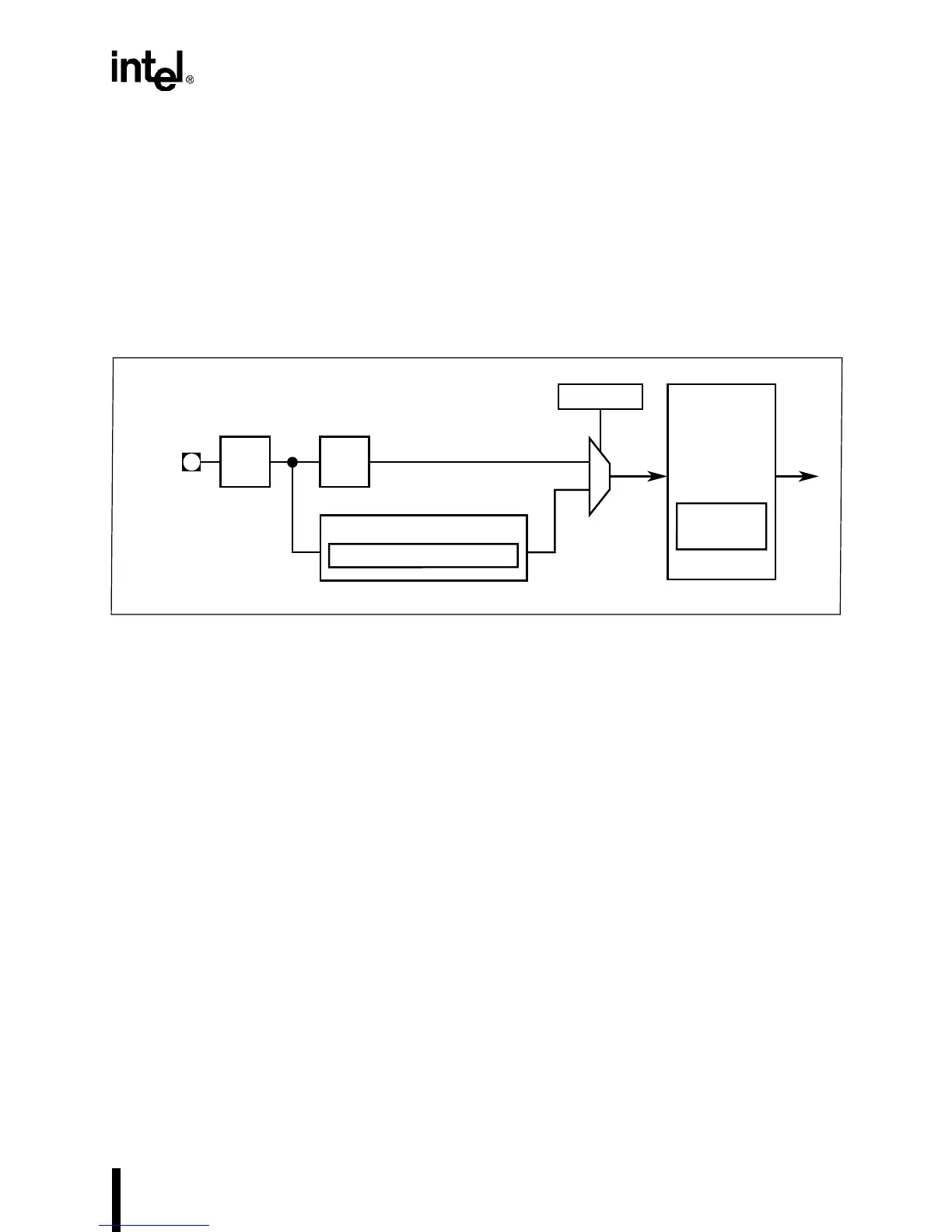

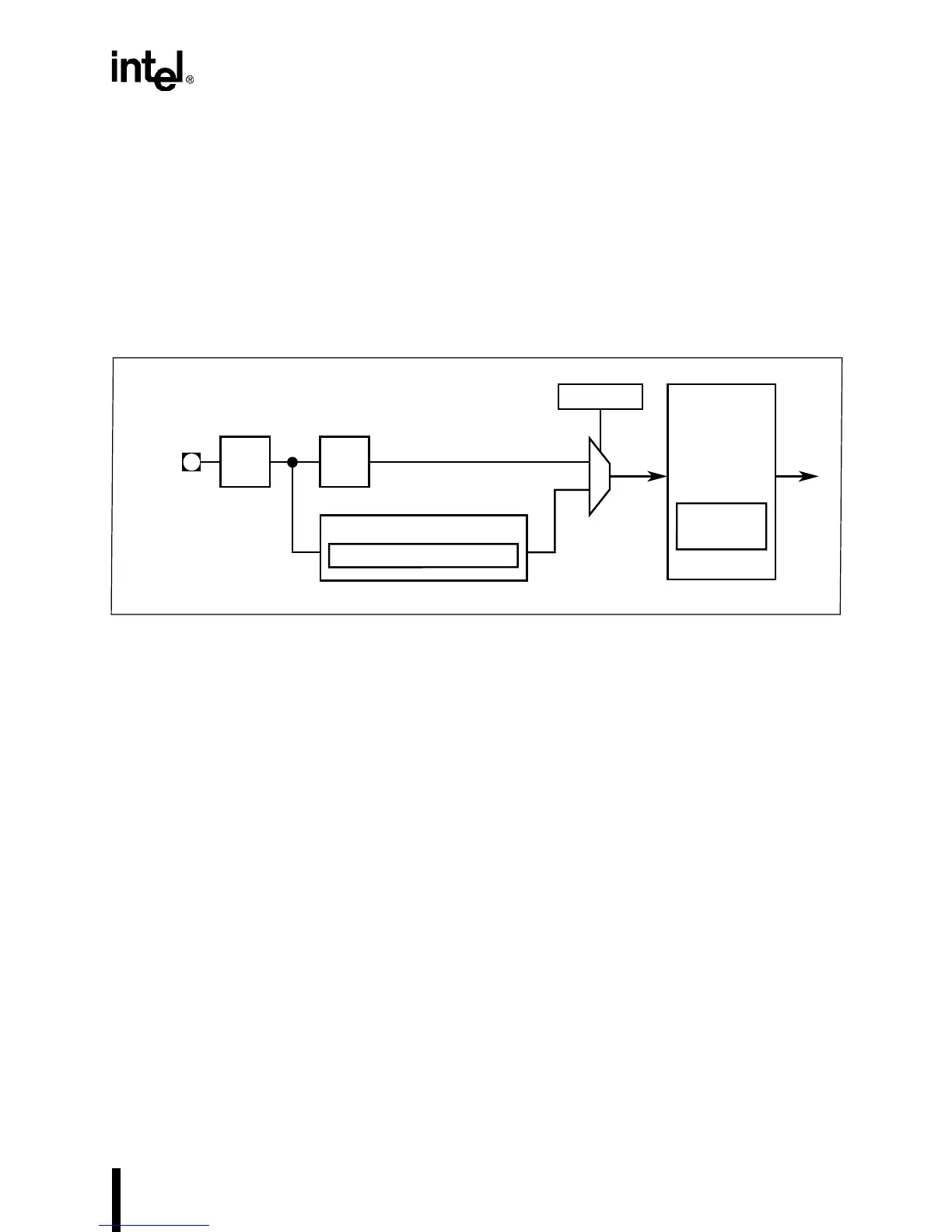

Either the prescaled clock or the serial clock (PSCLK or SERCLK) can drive the baud-rate gen-

erator (Figure 13-5). The SIO and SSIO configuration register (SIOCFG) selects one of these

sources.

Figure 13-5. Clock Sources for the Baud-rate Generator

OR

SERCLK provides a baud-rate input frequency (BCLKIN) of CLK2/4. The PSCLK frequency

depends on the 9-bit programmable divider. The input to the programmable divider is divided by

a 9-bit prescale value + 2.

A prescale value of 0 gives the maximum PSCLK frequency (CLK2/4) and a prescale value of

1FFH (511) gives the minimum PSCLK frequency (CLK2/1026).

A2443-02

1

0

Baud-rate

Generator

BCLKIN

÷ 2÷ 2

9-bit Programmable Divider

CLK2

SERCLK

PSCLK

SIOCFG.2

CLKPRS

SSIOBAUD

BV6:0

BCLKIN SERCLK

CLK2

4

----------------==

BCLKIN PSCLK

CLK2/2

prescale value 2+

------------------------------------------------==

Loading...

Loading...