A-3

SIGNAL DESCRIPTIONS

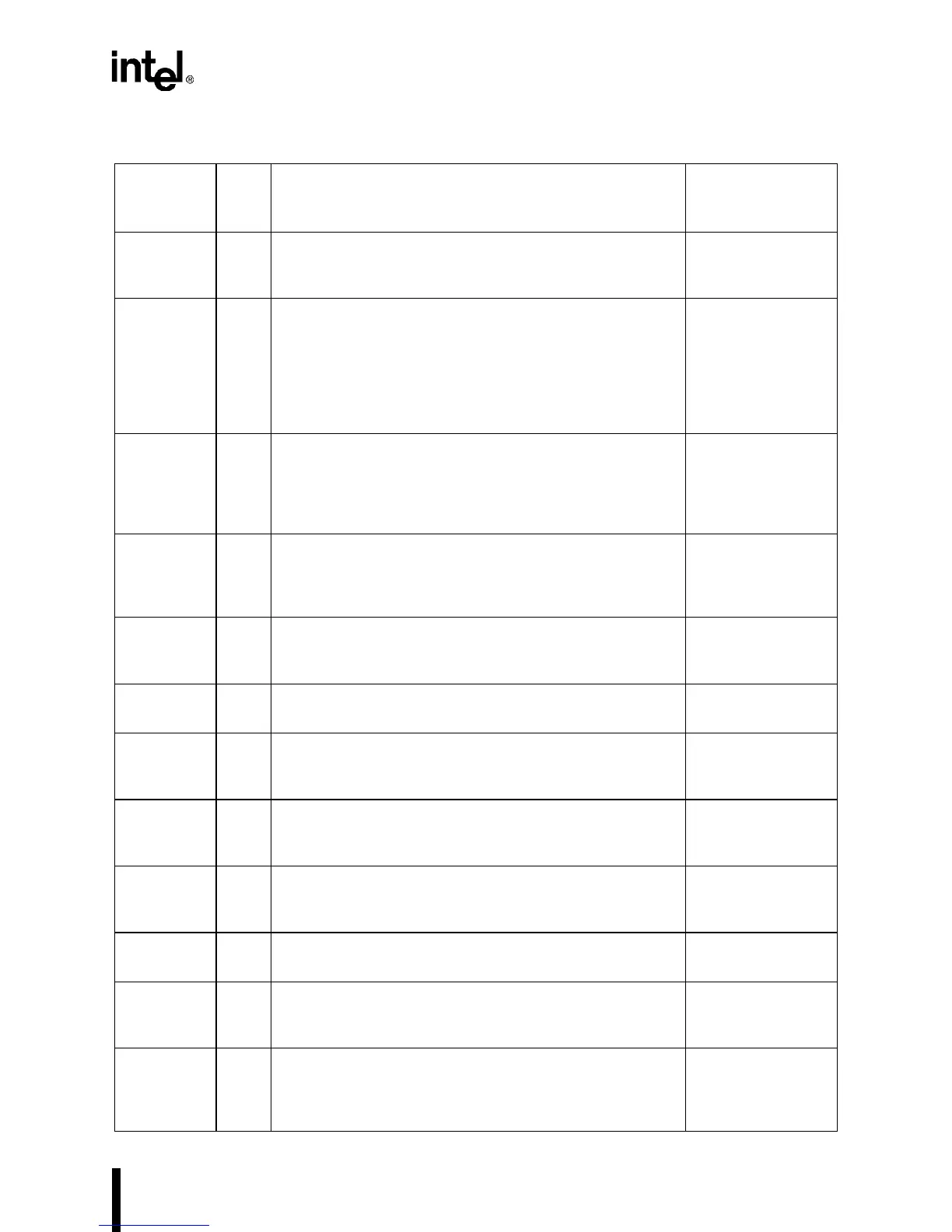

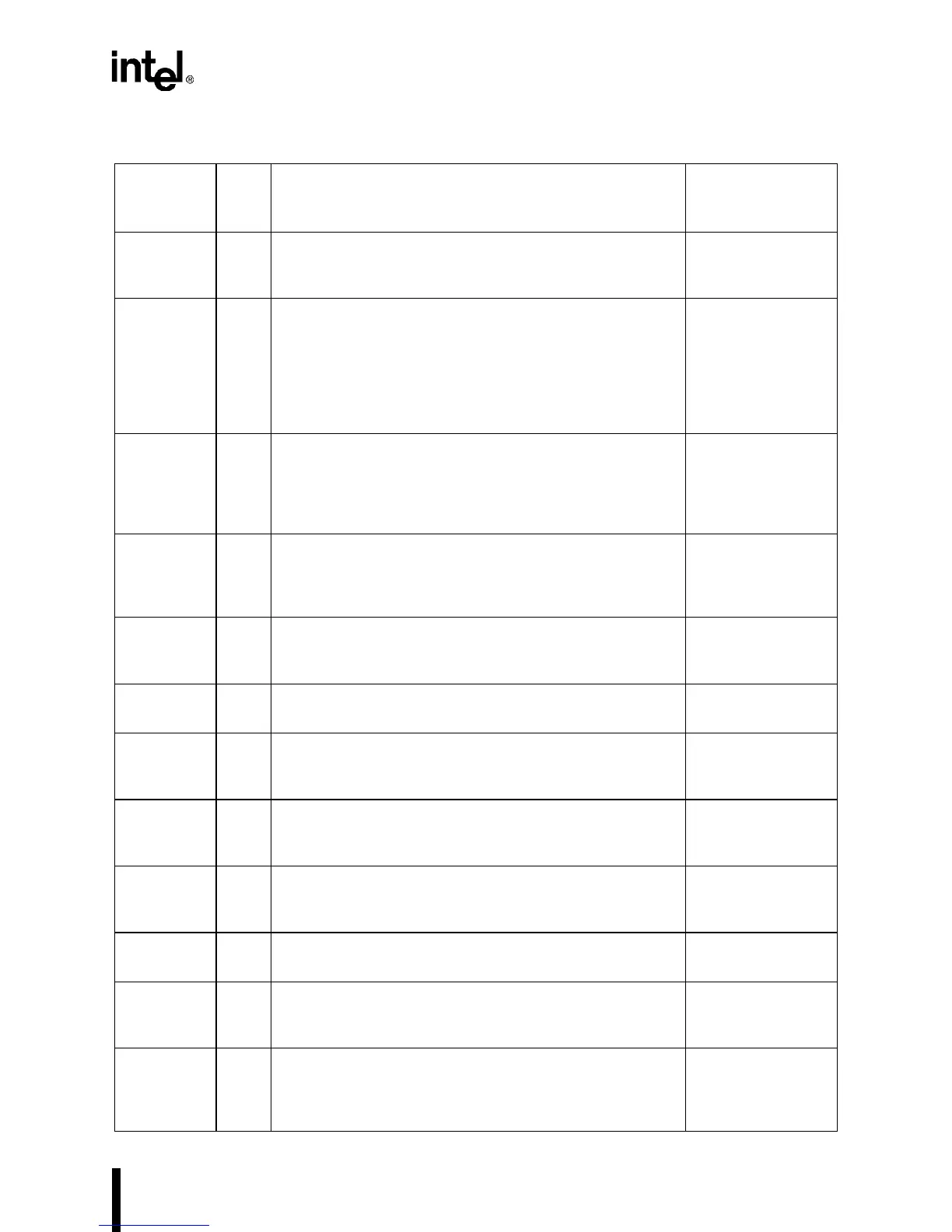

CTS1#

CTS0#

I Clear to Send:

Indicates that the modem or data set is ready to exchange

data with the SIO channel.

EOP#

P2.7

D15:0 I/O Data Bus:

Inputs data during memory read, I/O read, and interrupt

acknowledge cycles; outputs data during memory write and

I/O write cycles. During reads, data is latched during the

falling edge of phase 2 of T2, T2P, or T2i. During writes, this

bus is driven during phase 2 of T1 and remains active until

phase 2 of the next T1, T1P, or Ti.

—

DACK1#

DACK0#

O DMA Channel Acknowledge:

Indicates that the DMA channel is ready to service the

requesting device. An external device uses the DRQ

n

pin to

request DMA service; the DMA uses the DACK

n

pin to

indicate that the request is being serviced.

TXD1

CS5#

D/C# O Data/Control:

Indicates whether the current bus cycle is a data cycle

(memory or I/O read or write) or a control cycle (interrupt

acknowledge, halt/shutdown, or code fetch).

—

DCD1#

DCD0#

I Data Carrier Detect:

Indicates that the modem or data set has detected the SIO

channel’s data carrier.

DRQ0

P1.0

DRQ1

DRQ0

I DMA External Request:

Indicates that an external device requires DMA service.

RXD1

DCD1#

DSR1#

DSR0#

I Data Set Ready:

Indicates that the modem or data set is ready to establish

the communications link with the SIO channel.

STXCLK

P1.3

DTR1#

DTR0#

O Data Terminal Ready:

Indicates that the SIO channel is ready to establish a

communications link with the modem or data set.

SRXCLK

P1.2

EOP# I/OD End-of-process:

As an input, this signal terminates a DMA transfer. As an

ouput, it indicates that a DMA transfer has completed.

CTS1#

ERROR# I Error:

Indicates the the math coprocessor has an error condition.

TMROUT2

FLT# I Float:

Forces all bidirectional and output signals except TDO to a

high-impedance state.

—

HLDA O Hold Acknowledge:

Indicates that the processor has relinquished local bus

control to another bus master in response to a HOLD

request.

P1.7

Table A-2. Description of Signals Available at the Device Pins (Sheet 2 of 6)

Signal Type Name and Description

Multiplexed With

(Alternate

Function)

Loading...

Loading...