A-9

SIGNAL DESCRIPTIONS

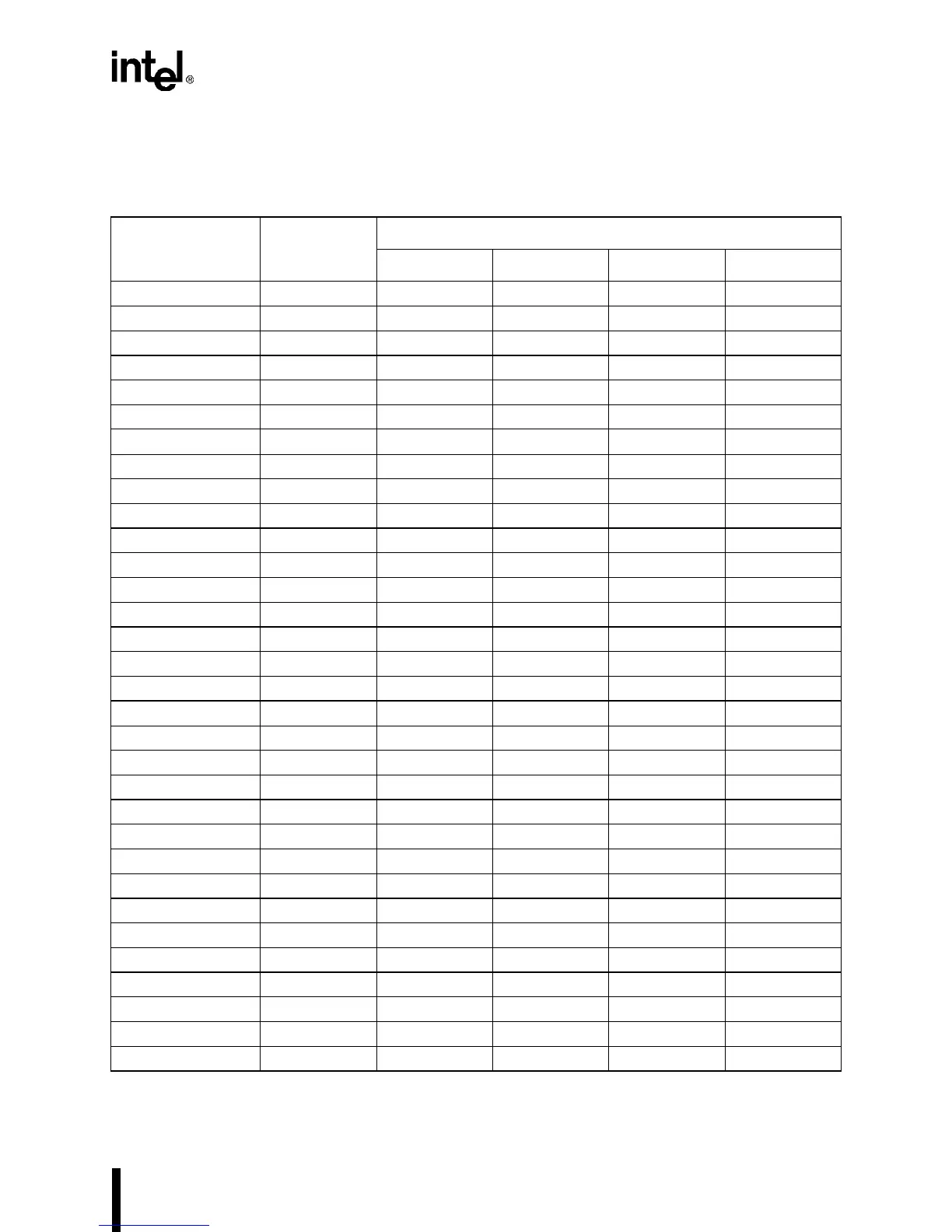

Table A-4 lists the states of output and bidirectional pins after reset and during idle mode, pow-

erdown, and hold.

Table A-4. Pin States After Reset and During Idle, Powerdown, and Hold (Sheet 1 of 2)

Symbol Type

Pin State

Reset Idle Powerdown Hold

A25:1 O111Z

ADS# O 1 1 1 Z

BHE# O 0 X 0 Z

BLE# O 0 X 1 Z

CAS2:0 O 1 1 1 Z

CLKOUT O Q Q 0 Q

CS4:0# O WH Q X 1

CS6:5# O 1 Q X 1

D15:0 I/OZZZZ

DACK1:0# O 1 Q X 1

D/C# O100Z

DTR1:0 O WH X X X

EOP# I/OD WH Z Z Z

HLDA O WL Q X 1

LBA# O 1 Q X 1

LOCK# O WH X X Z

M/IO# O 0 1 1 Z

P1.5:0 I/O WH X X X

P1.7:6 I/O WL X X X

P2.4:0 I/O WH X X X

P2.6:5 I/O WL X X X

P2.7 I/O WH X X X

P3.7:0 I/O WL X X X

PWRDWN O WL X 1 Q

RD# O1111

READY# I/OZZZZ

REFRESH# O 1 Q X 1

RTS1# O WL X X X

RTS0# O WH X X X

SMIACT# O 1 X X 1

SRXCLK I/O WH Q X or Q

(1)

Q

SSIOTX O WL Q X or Q

(1)

Q

NOTES:

1. X if clock source is internal; Q if clock source is external.

2. Q when shifting data out through the JTAG port, otherwise Z.

Loading...

Loading...