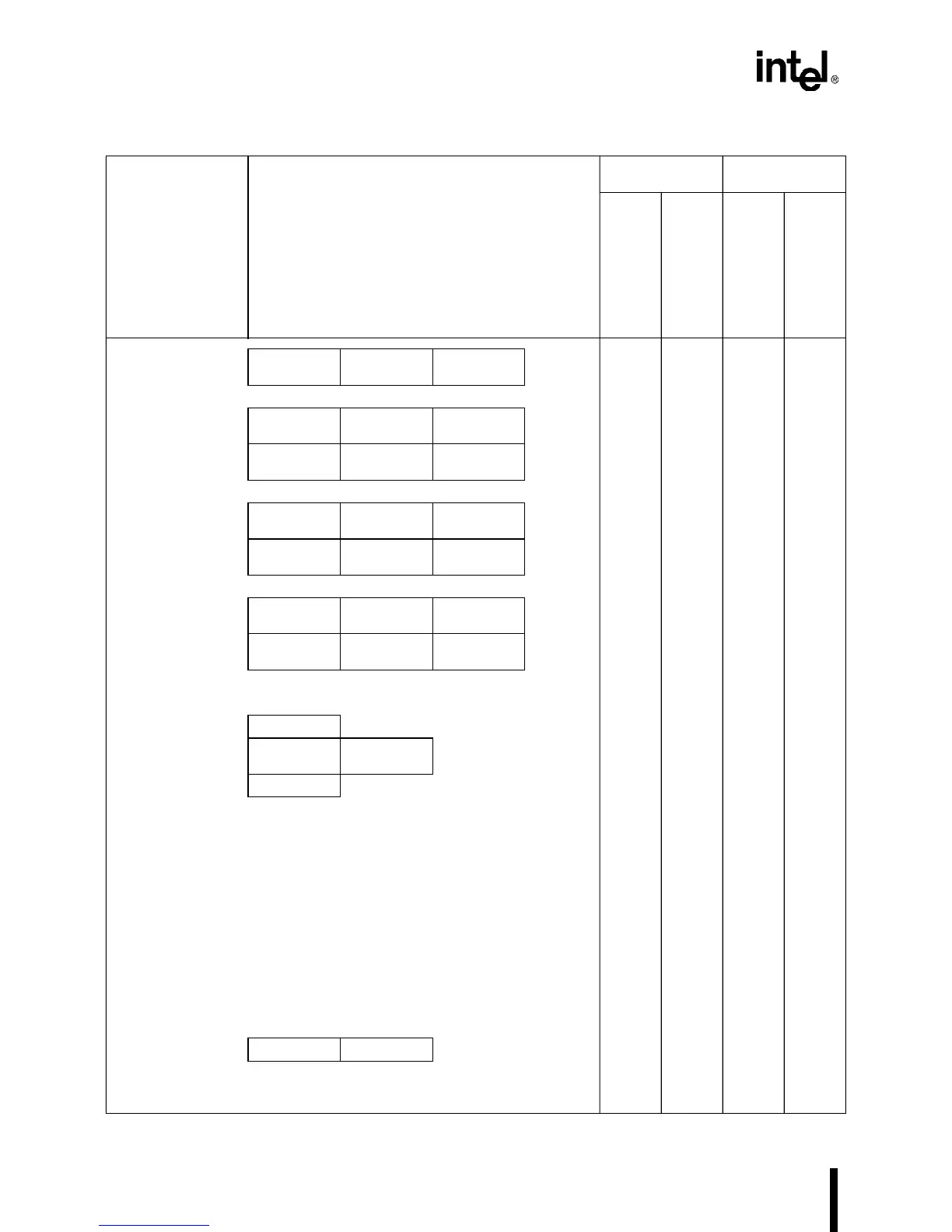

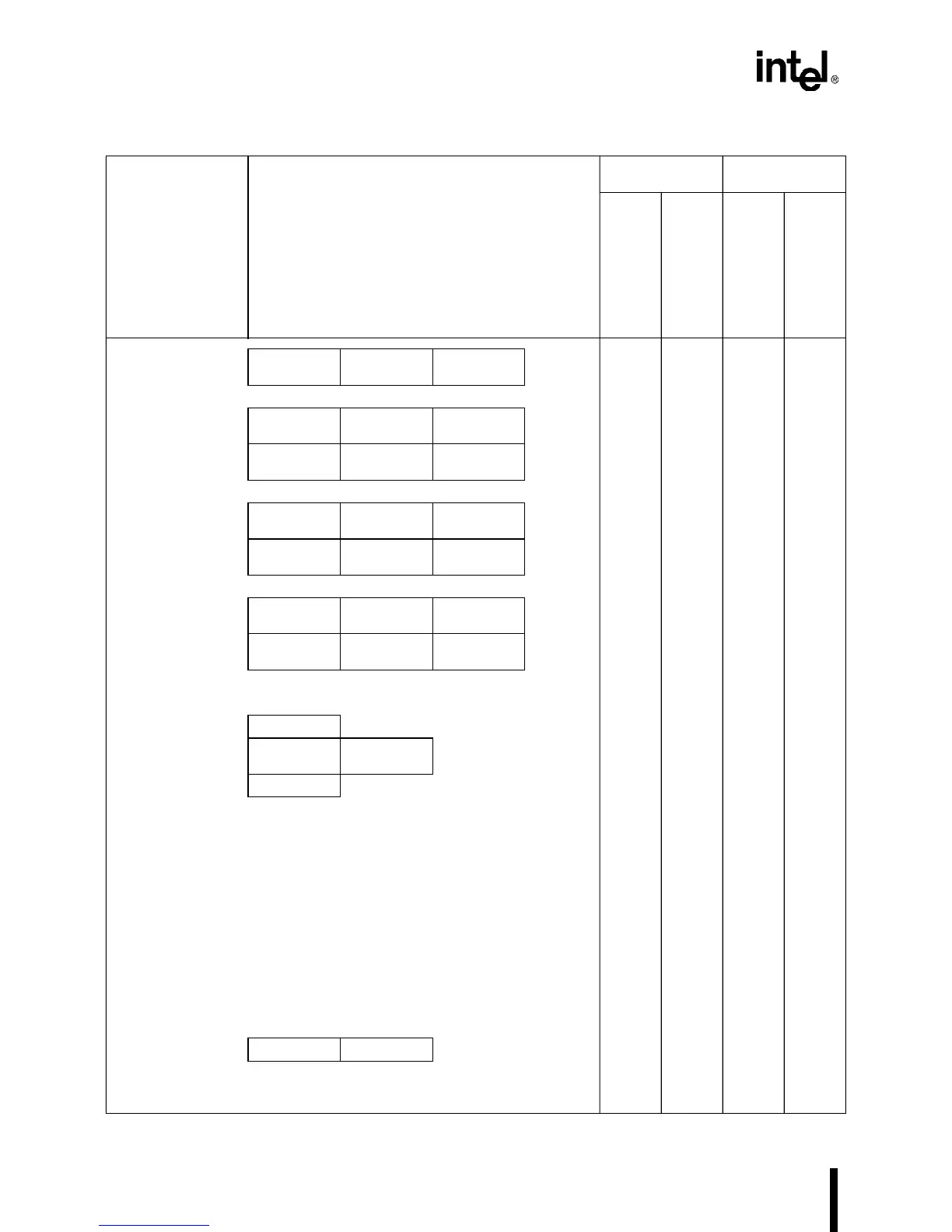

Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

E-10

register/memory,

register

0 0 0 0 1 1 1 1 1 0 1 0 0 0 1 1 mod reg r/m

3/12* 3/12* b h

BTC = test bit and complement

register/memory,

immediate

0 0 0 0 1 1 1 1 1 0 1 1 1 0 1 0 mod 1 1 1 r/m

immed

8-bit data

6/8* 6/8* b h

register/memory,

register

0 0 0 0 1 1 1 1 1 0 1 1 1 0 1 1 mod reg r/m

6/13* 6/13* b h

BTR = test bit and reset

register/memory,

immediate

0 0 0 0 1 1 1 1 1 0 1 1 1 0 1 0 mod 1 1 0 r/m

immed

8-bit data

6/8* 6/8* b h

register/memory,

register

0 0 0 0 1 1 1 1 1 0 1 1 0 0 1 1 mod reg r/m

6/13* 6/13* b h

BTS = test bit and set

register/memory,

immediate

0 0 0 0 1 1 1 1 1 0 1 1 1 0 1 0 mod 1 0 1r/m

immed

8-bit data

6/8* 6/8* b h

register/memory,

register

0 0 0 0 1 1 1 1 1 0 1 0 1 0 1 1 mod reg r/m

6/13* 6/13* b h

CONTROL TRANSFER

CALL = Call

direct within segment 1 1 1 0 1 0 0 0 full displacement 7 + m* 9 + m* b r

reg/memory indirect

within segment

1 1 1 1 1 1 1 1 mod 0 1 0 r/m

7 + m*/

10 + m*

9 + m*/

12 + m*

b h, r

direct intersegment 1 0 0 1 1 0 1 0 unsigned full offset, selector 17 + m* 42 + m* b j, k, r

Protected mode only (direct intersegment)

Via call gate to same privilege level 64 + m h, j, k, r

Via call gate to different privilege level (no parameters) 98 + m h, j, k, r

Via call gate to different privilege level (x parameters) 106+8x+

m

h, j, k, r

From 286 task to 286 TSS 285 h, j, k, r

From 286 task to Intel386 SX CPU TSS 310 h, j, k, r

From 286 task to virtual 8086 task (Intel386 SX CPU TSS) 229 h, j, k, r

From Intel386 SX CPU task to 286 TSS 285 h, j, k, r

From Intel386 SX CPU task to Intel386 SX CPU TSS 392 h, j, k, r

From Intel386 SX CPU task to Virtual 8086 task (Intel386 SX CPU TSS) 309 h, j, k, r

indirect intersegment 1 1 1 1 1 1 1 1 mod 0 1 1 r/m 30 + m 46 + m b h, j, k, r

Protected mode only (indirect intersegment)

Via call gate to same privilege level 68 + m h, j, k, r

Table E-1. Instruction Set Summary (Sheet 9 of 19)

Instruction Format

Clock Count Notes

Real

Ad-

dress

Mode

or

Virtual

8086

Mode

Pro-

tected

Virtual

Ad-

dress

Mode

Real

Ad-

dress

Mode

or

Virtual

8086

Mode

Pro-

tected

Virtual

Ad-

dress

Mode

Loading...

Loading...