150

Intel

®

855GME Chipset and Intel

®

6300ESB ICH Embedded Platform Design Guide

System Memory Design Guidelines (DDR-SDRAM)

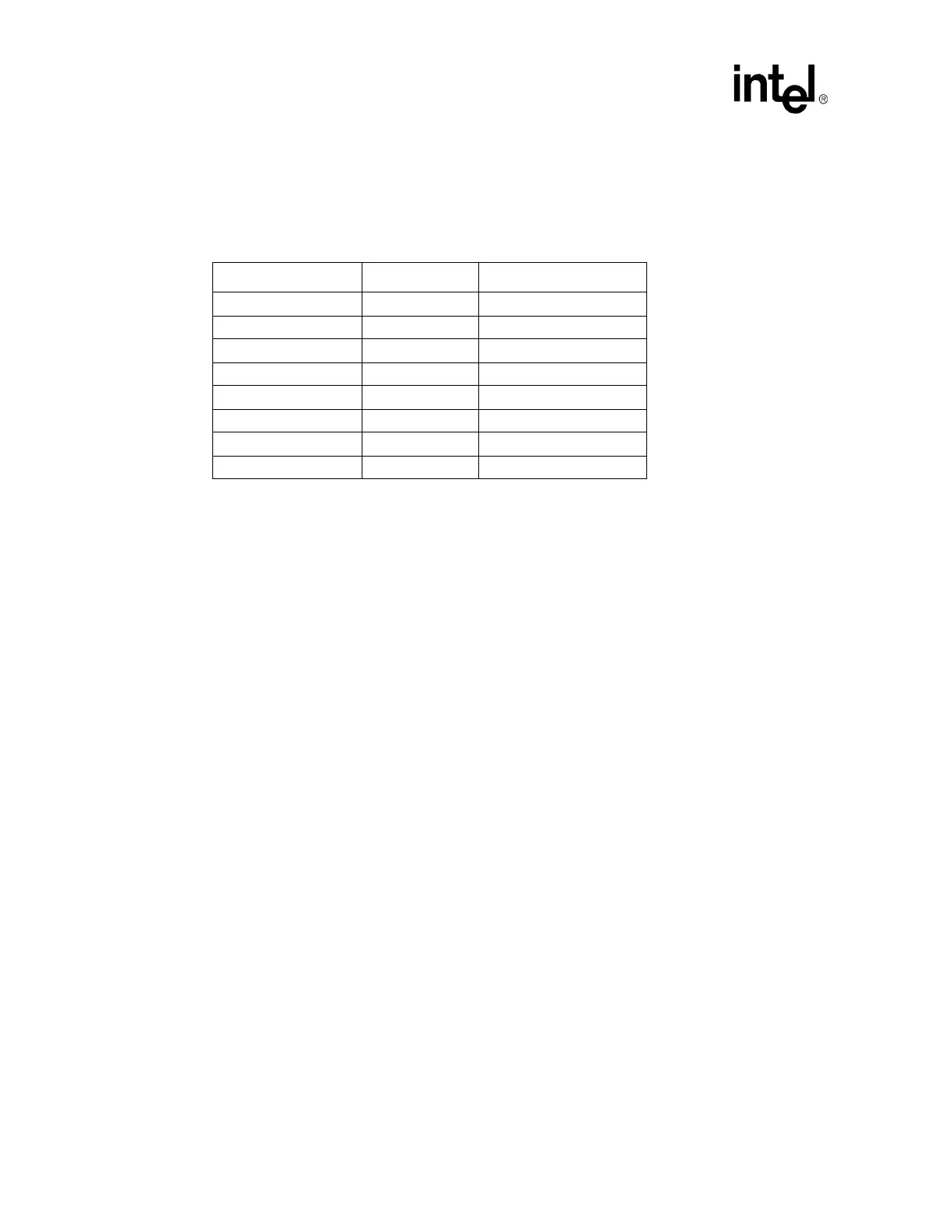

5.4.7.4 CPC Group Package Length Table

The package length data in Table 42 shall be used to match the overall length of each CPC signal to

its associated clock reference length.

5.4.8 Feedback – RCVENOUT#, RCVENIN#

The 82855GME provides a feedback signal called ‘receive enable’ (RCVENIN#), which is used to

measure timing for memory read data. The Intel 855GME chipset has the RCVENOUT# signal

shunted directly to RCVENIN# inside the package to reduce timing variation. With this change it is

no longer necessary to provide an external connection. However, it is recommended that both

signals be transitioned to the bottom side with vias located adjacent to the package ball in order to

facilitate probing.

5.5 ECC Guidelines

The GMCH may be configured to operate in an ECC data integrity mode that allows multiple bit

error detection and single bit error correction. This option to design for and support ECC DDR

memory modules is dependent on design objectives. By default ECC functionality is disabled on

the platform.

For more information on ECC functionality, see the

Intel® 855GME Chipset Graphics and

Memory Controller Hub (GMCH) Specification Update Addendum for Embedded Applications.

5.5.1 GMCH ECC Functionality

When non-ECC memory modules are to be the only supported memory type on the platform, the

eight DDR check bits signals, associated strobe and data mask bit associated with the ECC device

for each DIMM may be left as no connects on the GMCH.

Table 42. CPC Group Package Lengths

Signal Pin Number Pkg Length (mils)

SMA[1] AD14 398

SMA[2] AD13 443

SMA[4] AD11 430

SMA[5] AC13 346

SMAB[1] AD16 427

SMAB[2] AC12 395

SMAB[4] AF11 716

SMAB[5] AD10 631

Loading...

Loading...