88

Intel

®

855GME Chipset and Intel

®

6300ESB ICH Embedded Platform Design Guide

4.3.4.2 Processor PLL Voltage Supply Power Sequencing

Refer to Section 4.8 for more details on platform power sequencing requirements for the 1.8 V

supply to the Intel Pentium M/Celeron M processor PLLs.

4.3.4.3 Processor PLL Decoupling Requirements

Table 20 presents the V

CCA[3:0]

decoupling guidelines.

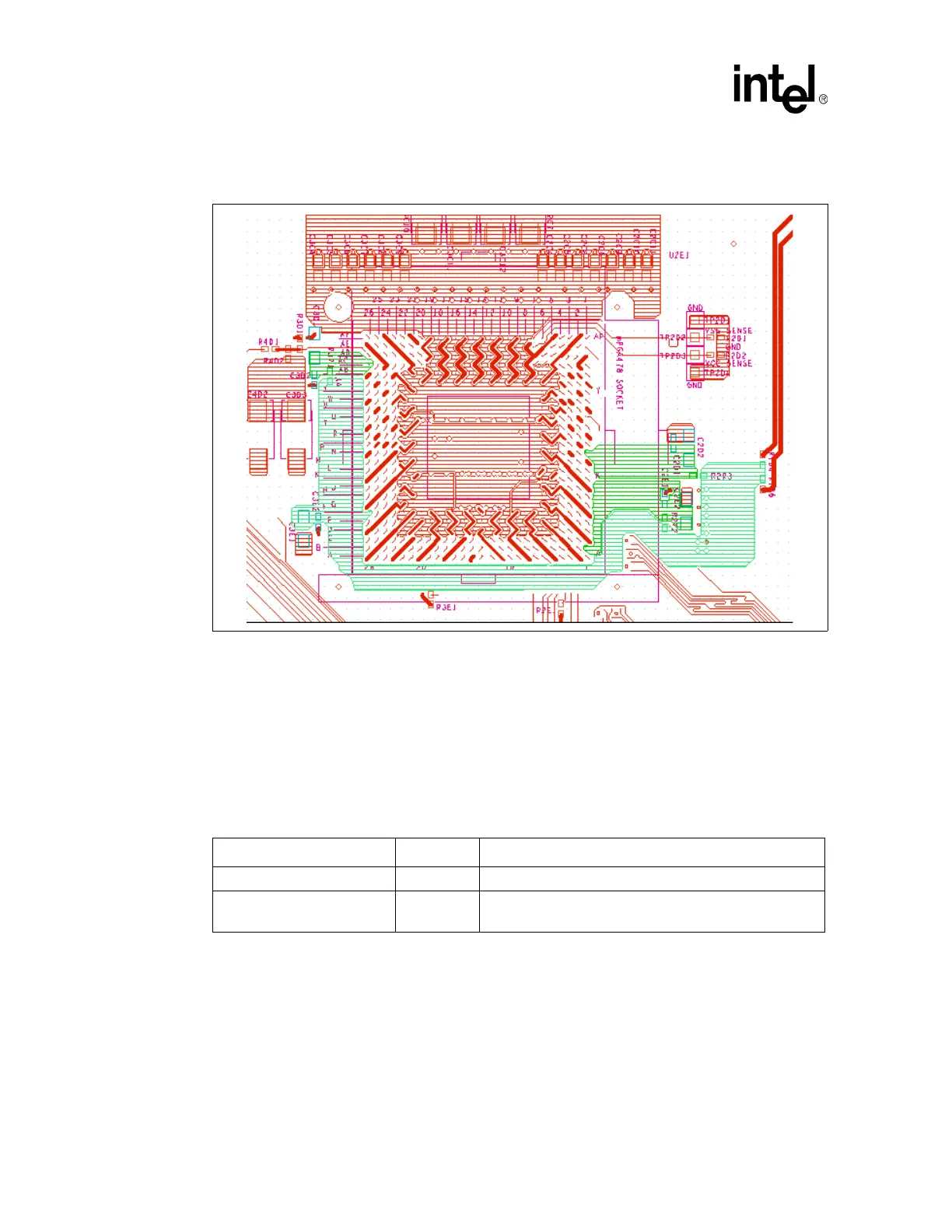

Figure 41. Intel

®

Pentium

®

M/Celeron

®

M Processor 1.8 V Intel

®

Customer Reference Board

Routing Example

Table 20. V

CCA[3:0]

Decoupling Guidelines

Description Cap (µF) Notes

Mid-Frequency Decoupling 4 x 10 µF (Polymer Covered Tantalum – POSCAP, Neocap, KO Cap)

High-Frequency Decoupling 4 x 10 nF

(0603 MLCC, >= X7R)

Place next to the Intel Pentium M/Celeron M processor CPU.

NOTES:

1. VCCA[3:0] should be tied to Vcc1_8S.

2. One 10 µF and one 10 nF capacitor pair should be used for each VCCA pin.

Loading...

Loading...