74

Intel

®

855GME Chipset and Intel

®

6300ESB ICH Embedded Platform Design Guide

4.1.11 Pentium

®

M/Celeron

®

M Processor V

CCSENSE

/V

SSSENSE

Design Recommendations

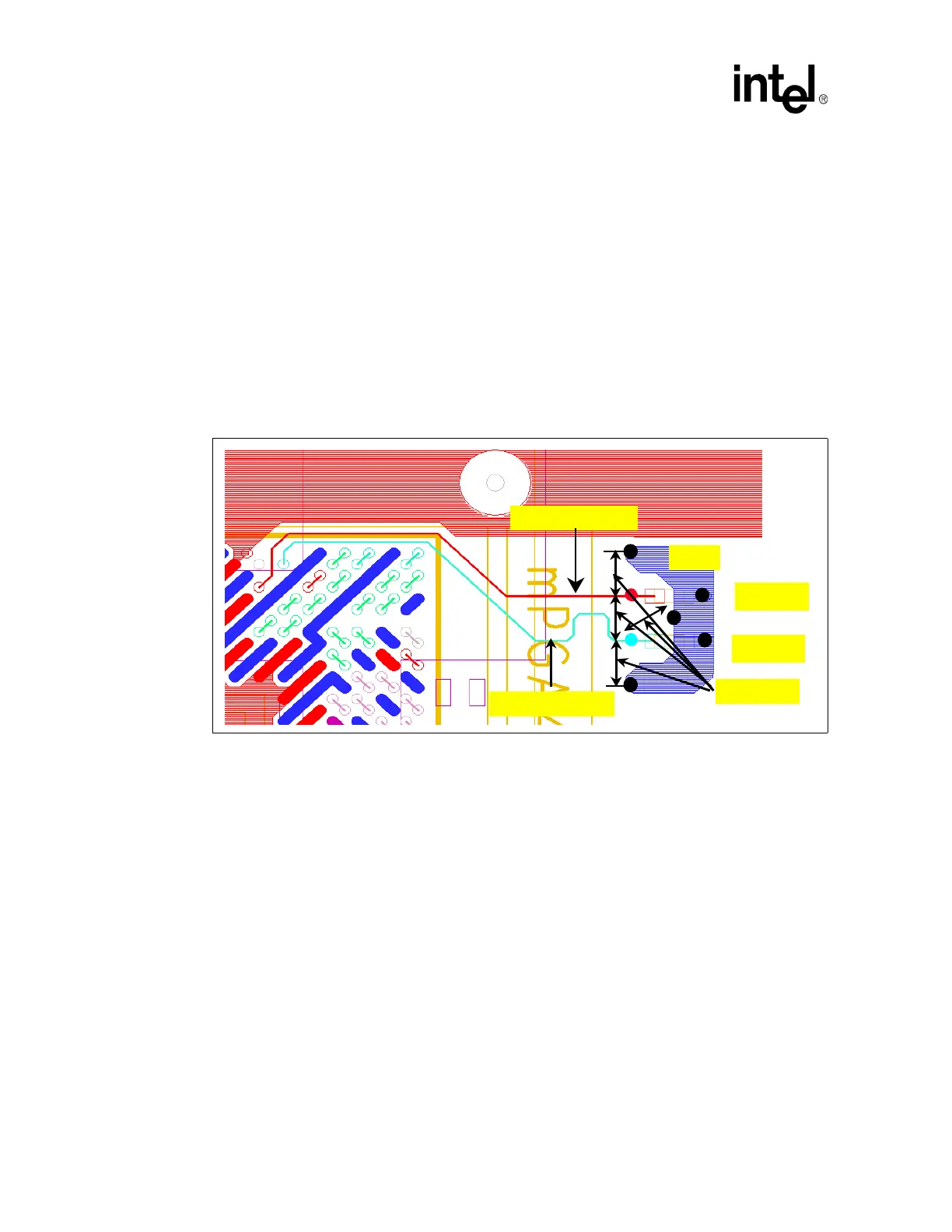

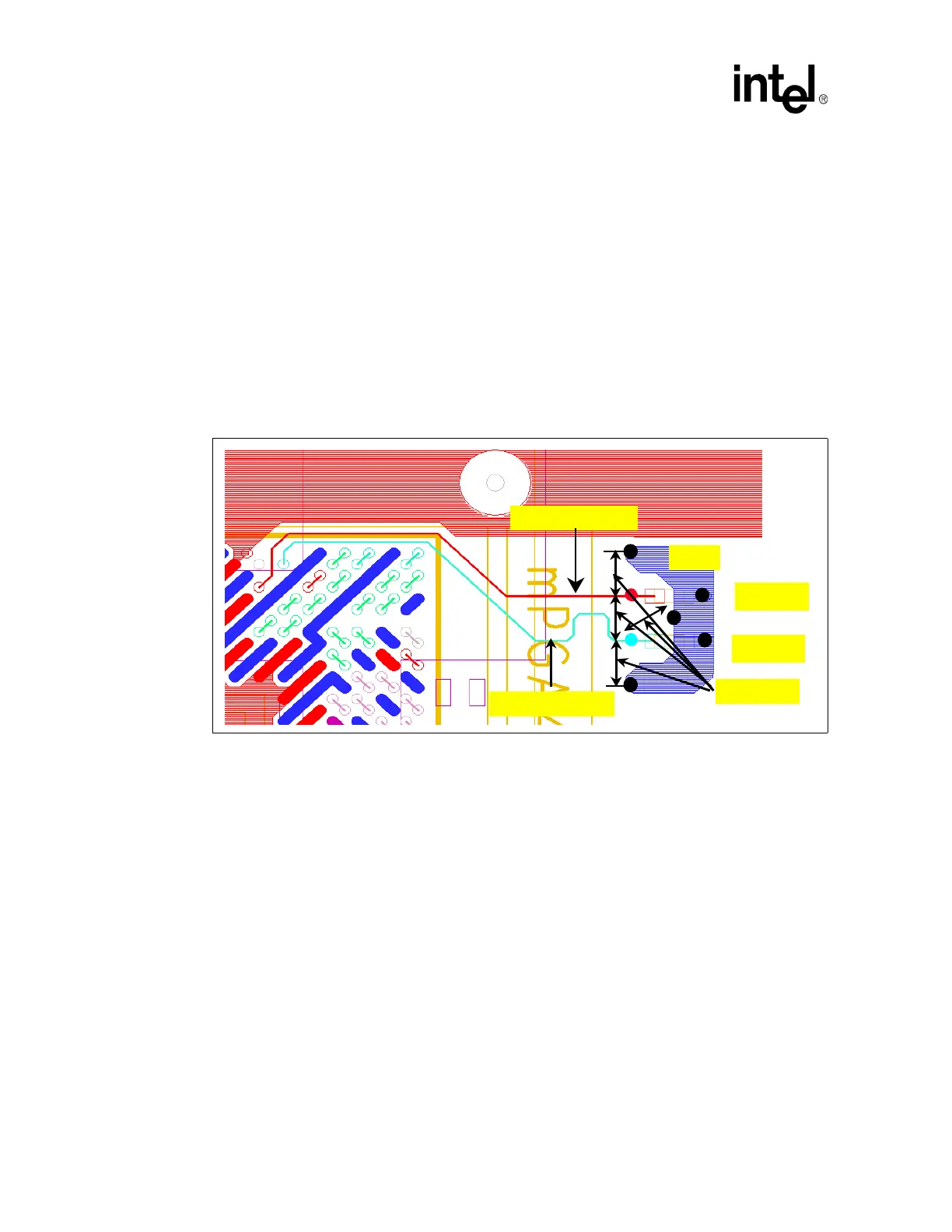

The VCCSENSE and VSSSENSE signals of the Intel Pentium M/Celeron M processor provide

isolated, low impedance connections to the processor’s core power (VCC) and ground (VSS).

These pins may be used to sense or measure power (VCC) or ground (VSS) near the silicon with

little noise. To make them available for measurement purposes, it is recommended that

VCCSENSE and VSSSENSE both be routed with a Zo = 55

Ω ± 15 percent trace of equal length.

Use 3:1 spacing between the routing for the two signals and all other signals shall be a minimum of

25 mils (preferably 50 mils) from VCCSENSE and VSSSENSE routing. Terminate each line with

an optional (default is No Stuff) 54.9

Ω ± 1 percent resistor. Also, a ground via spaced 100 mils

away from each of the test point vias for VCCSENSE and VSSSENSE shall be added. A third

ground via shall also be placed in between them to allow for a differential probe ground. Refer to

Figure 35 for the recommended layout example.

4.1.12 PLL Voltage Design for Low Voltage Intel

®

Pentium

®

M

Processors on 90 nm process with 2 MB L2 Cache

One primary difference between the Intel Pentium M processor (130nm) and the Low Voltage

Intel

®

Pentium

®

M Processor on 90 nm process with 2 MB L2 cache or the Intel

®

Celeron

®

M

Processor on 90nm process is the analog PLL voltage supplying the processor’s on-die clock

generators. The VCCA PLL power delivery pins of the Low Voltage Intel Pentium M Processors

on 90 nm process with 2 MB L2 cache and the Intel

®

Celeron

®

M Processor on 90nm process have

the option of using either a 1.8 V or 1.5 V power supply. For a platform supporting only Low

Voltage Intel Pentium M Processors on 90 nm process with 2 MB L2 cache or Intel

®

Celeron

®

M

Processor on 90nm process, the VCCA[3:0] pin should be powered by the 1.5 V rail, since the 1.5

V rail is already required for GMCH. This eliminates the need for a 1.8 V rail on the platform.

However, if a platform is to also support Intel Pentium M processors (130nm) and standard voltage

Intel

®

Pentium

®

M Processors on 90 nm process with 2 MB L2 cache, then the 1.8 V rail must be

used for the analog PLL voltage supply.

Figure 35. V

CCSENSE

/V

SSSENSE

Routing Example

GND

54.9

Ω

54.9

Ω

100 mil

Loading...

Loading...