80

Intel

®

855GME Chipset and Intel

®

6300ESB ICH Embedded Platform Design Guide

2. Reference these signals to ground planes and avoid routing across power plane splits.

3. The number of routing layer transitions should be minimized. When layout constraints require

a routing layer transition, any such transition shall be accompanied with ground stitching vias

placed within 100 mils of the signal via with at least one ground via for every two signals

making a layer transition.

DBR# should be routed to the system reset logic (e.g., the SYSRST# signal of the 6300ESB) and

initiate the equivalent of a front panel reset commonly found in desktop systems. The 150

Ω to

240

Ω pull-up resistor should be placed within 1 ns of the ITP700FLEX connector.

Note: The CPU should not be power cycled when DBR# is asserted.

DBA# is an optional system signal that may be used to indicate to the system that the ITP/TAP port

is being used. When not implemented, this signal may be left as no connect. When implemented, it

shall be routed with a 150

Ω to 240 Ω pull-up resistor placed within 1 ns of the ITP700FLEX

connector. Refer to the ITP700 Debug Port Design Guide for more details on DBA# usage.

The ITP700FLEX VTT and VTAP pins should be shorted together and connected to the VCCP

(1.05 V) plane with a 0.1 µF decoupling capacitor placed within 0.1 inch of the VTT pins. Table 19

summarizes termination resistors values, placement, and voltages the ITP signals need to connect

to for proper operation for onboard ITP700FLEX debug port.

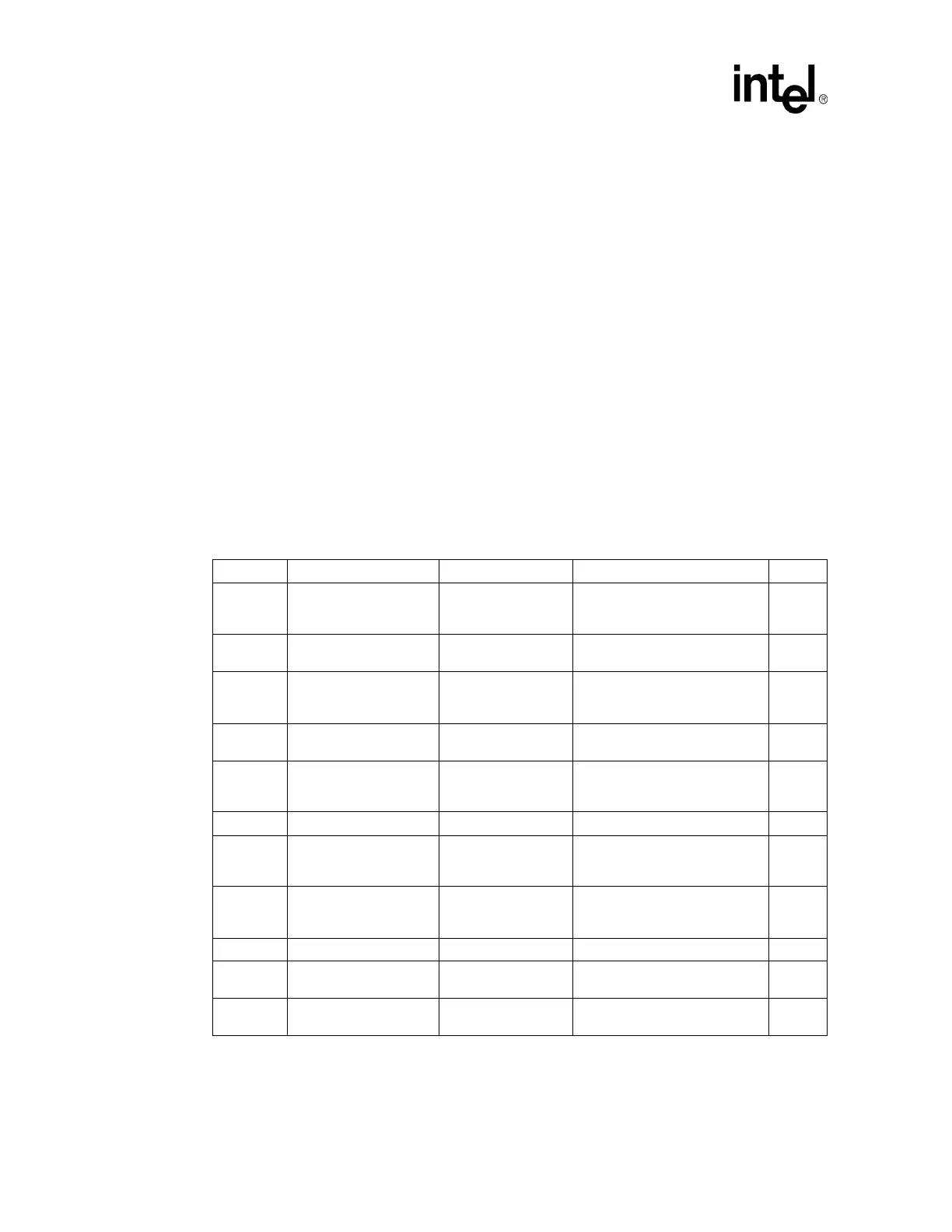

Table 19. Recommended ITP700FLEX Signal Terminations (Sheet 1 of 2)

Signal Termination Value Termination Voltage Termination/Decap Location Notes

TDI 150 Ω ± 5% VCCP (1.05 V)

Within ± 300 ps of the Intel

Pentium M/Celeron M processor

CPU TDI pin

5

TMS 39.2

Ω ± 1% VCCP (1.05 V)

Within ± 200 ps of the

ITP700FLEX connector TMS pin

5

TRST# 510-680

Ω ±5% GND

Anywhere between Intel Pentium

M/Celeron M processor CPU and

ITP700FLEX connector

5

TCK 27.4

Ω ±1% GND

Within ± 200 ps of the ITP700

FLEX connector TCK pin

5

TDO

54.9

Ω ± 1% pull-up and

22.6

Ω ±1% series

resistor

VCCP (1.05 V)

Within 1” of the ITP700FLEX

connector TDO pin

1, 5

BCLK(p/n) 2

FBO

Connect to TCK pin of

Intel Pentium M/Celeron

M processor CPU

N/A N/A 1

RESET#

220

Ω ± 5% pull-up and

22.6

Ω ±1% series

resistor

VCCP (1.05 V)

Within 0.5” of the ITP700FLEX

connector RESET# pin

1

BPM[5:0]# Not Required 3

DBA# 150-240

Ω ±5%

VCC of target system

recovery circuit

Within 1 ns of the ITP700FLEX

connector DBA# pin

4

DBR# 150-240

Ω ±5%

VCC of target system

recovery circuit

Within 1 ns of the ITP700FLEX

connector DBR# pin

Loading...

Loading...