232

Intel

®

855GME Chipset and Intel

®

6300ESB ICH Embedded Platform Design Guide

Intel

®

6300ESB Design Guidelines

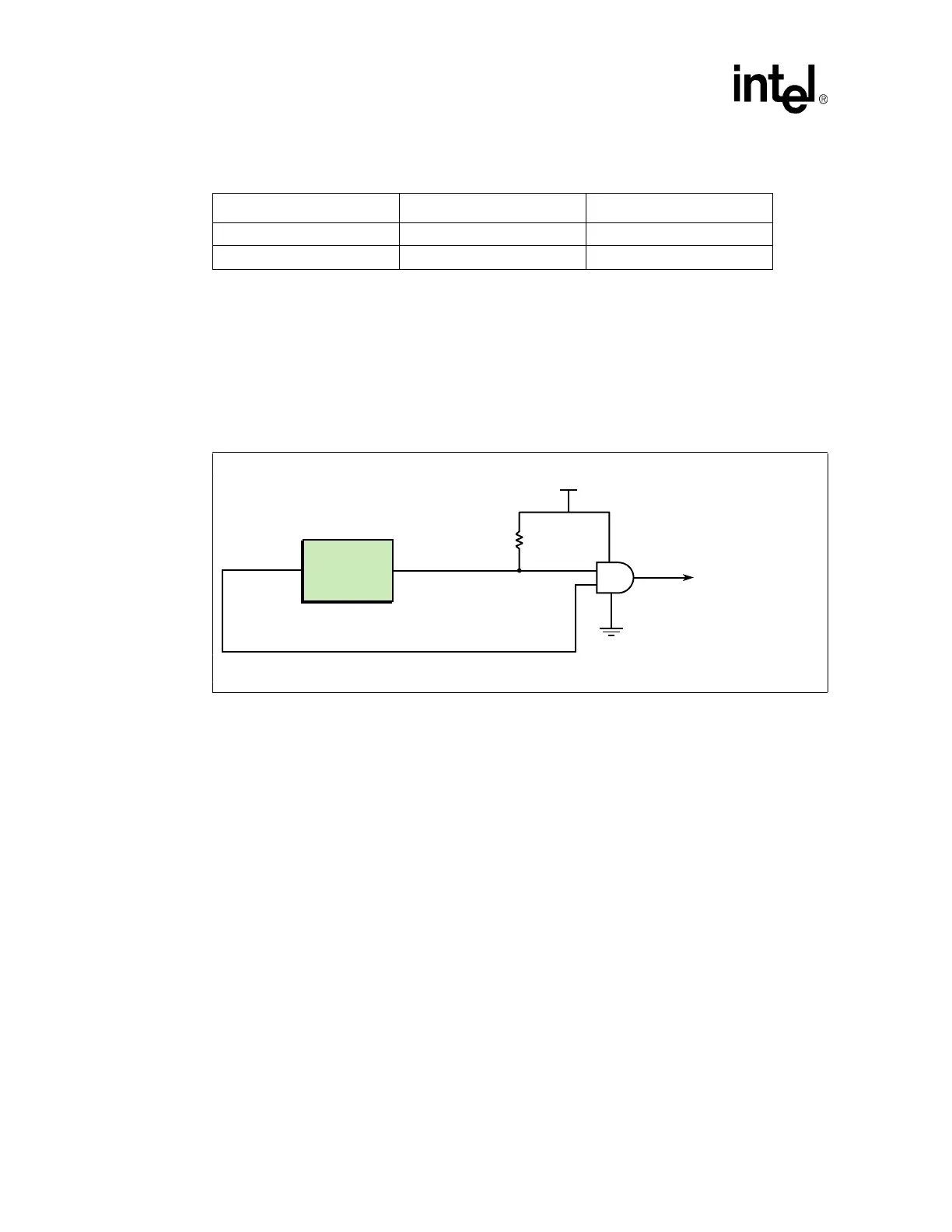

9.10.3 PCI-X Secondary Bus Reset

The Secondary Bus Reset (SBR) function on the 6300ESB enables the user to change the mode and

frequency of the PCI-X Bus without resetting the entire system. If this function is not needed in the

system design refer to Section 9.10.3.1. When utilizing the SBR function an external circuit is

required. Refer to Figure 126 for proper implementation:

NOTE: Recommended pull-up resistor value (R) is 100 KΩ −200 KΩ

9.10.3.1 Secondary Bus Reset Not Utilized

When the SBR function on the 6300ESB is not utilized the following should be considered:

• The SBR pin PCIXSBRST# (Ball AA7) may be left as a No Connect

• The PCI-X slots should be tied to the system reset logic (PXPCIRST#)

9.10.4 PME# Signal Sharing

In many cases the system designer will choose to share the PME# signal between the PCI-X bus

and the PCI bus. While this option has been tested, certain considerations must be made when

using this configuration.

9.10.4.1 Issues with Sharing PME#

Many operating systems recommend that the PME# signal is not shared when designing an optimal

system. Refer to your specific operating system for issues that may occur when routing a shared

PME# signal.

Table 100. IDSEL to PXAD Bit Assignment

Slot # PXAD Bit Device Number

1171

2182

Figure 126. Usage Model for SBR Functionality

B2849-01

GND

R

PCIXSBRST#

pin to slot

PXPCIRST# PCIXSBRST#

Vcc_suspend

AND

Intel

®

6300ESB I/O

Controller

Loading...

Loading...