January 2007 307

Intel

®

855GME Chipset and Intel

®

6300ESB ICH Embedded Platform Design Guide

Layout Checklist

13.2 Intel

®

855GME Chipset GMCH (82855GME)

Layout Checklist

Table 149 presents the Intel

®

855GME chipset GMCH layout checklist.

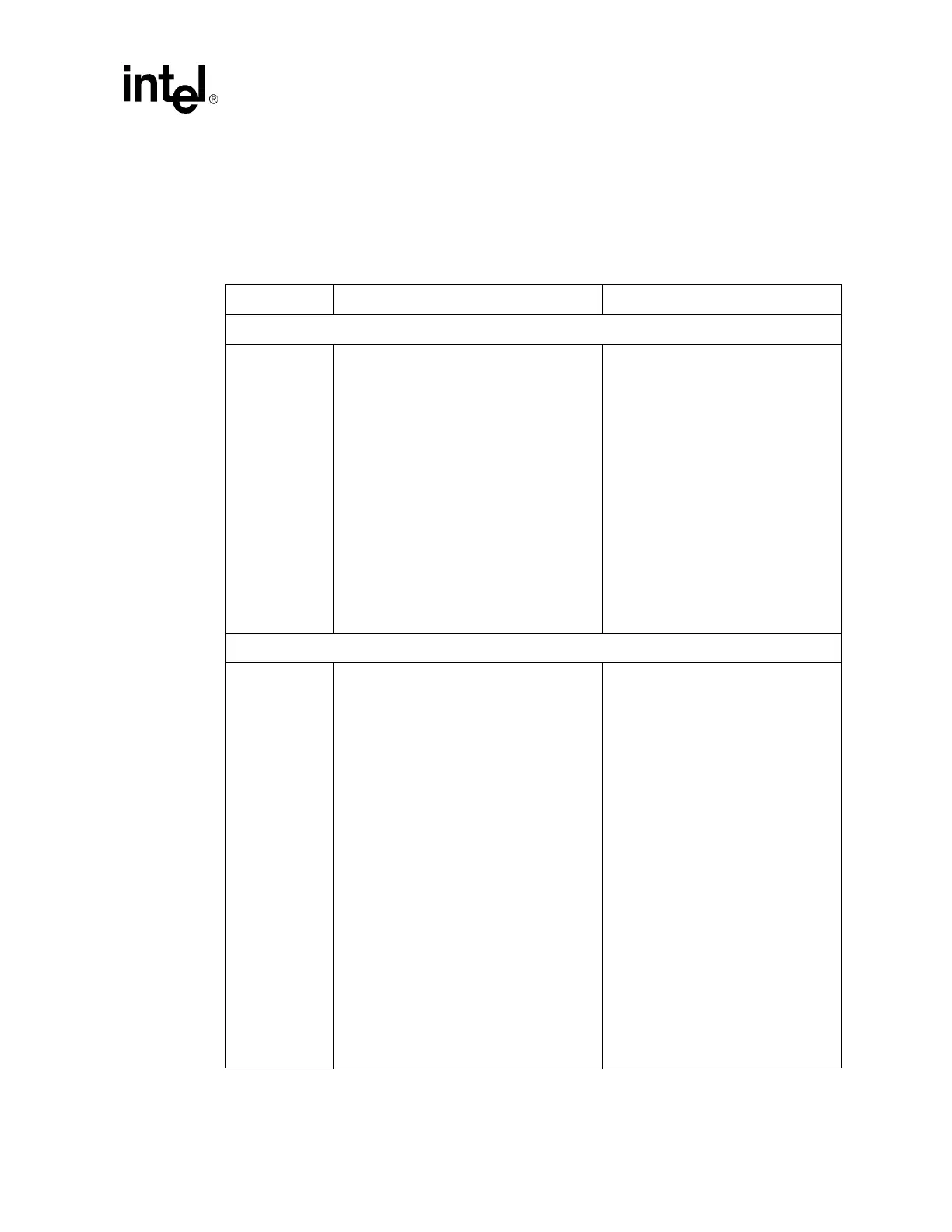

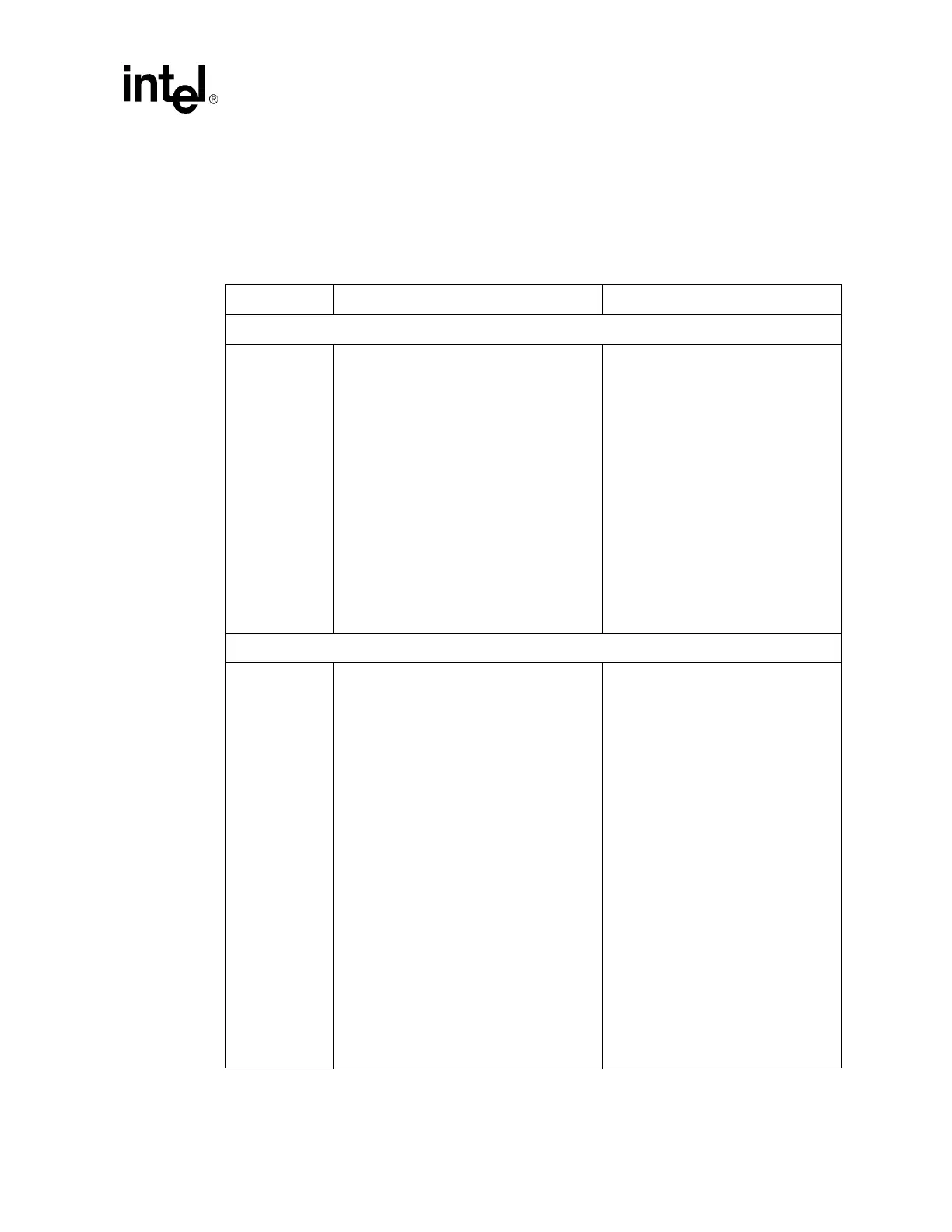

Table 149. Intel

®

855GME Chipset GMCH Layout Checklist (Sheet 1 of 6)

Checklist Items Recommendations Comments

Host Interface

Signals

ADS#

BNR#

BPRI#

BREQ0#

1

CPURST#

2

DBSY#

DEFER#

HA[31:3]#

3

HD[63:0]#

4

HADSTB[1:0]#

5

HDSTBN[3:0]#

6

HDSTBP[3:0]#

7

HIT#

HITM#

HLOCK#

10

HREQ[4:0]#

8

HTRDY#

9

DRDY#

RS[2:0]#

DINV[3:0]#

• Refer to the Processor section of this

checklist.

DDR System Memory Interface

SCK[5:0]

SCK[5:0]#

• Refer to the detailed discussion on this

topic in Section 5.4.3

• Route as closely-coupled differential pairs,

3 clock pairs to each DIMM.

• Spacing to other DDR signals should not

be less than 20 mils. Isolation from non-

DDR signals should be 25 mils.

• Route on internal layers, except for pin

escapes.

• Nominal internal trace width 7 mils and

nominal internal spacing 4 mils.

• Routed trace length limits are 3.5 to 6.5

inches.

• Length match clock pairs to ±10 mils.

• Match all DIMM0 clocks to X0 ± 25 mils

• Match all DIMM1 clocks to X1 ± 25 mils

• Match all DIMM0 clock lengths and match

all DIMM1 clock lengths.

• Use GMCH package lengths for pad-to-

pin length tuning.

• Differential mode impedance is

70 ohms ± 15%

• Maximum breakout length is 0.3 inches

• Maximum via count of 2 per side

• Refer to the detailed routing

guidelines in Section 5.4.3.

Loading...

Loading...