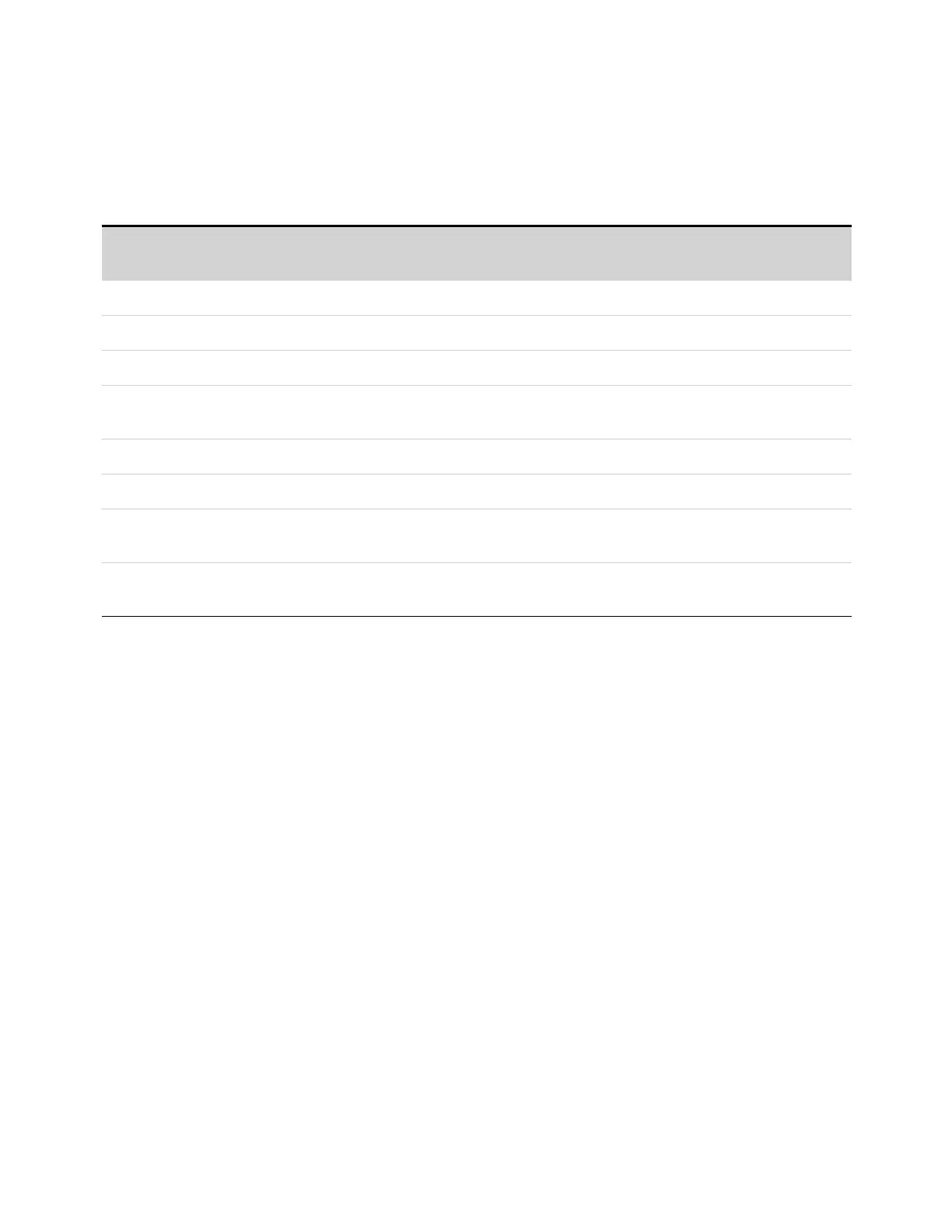

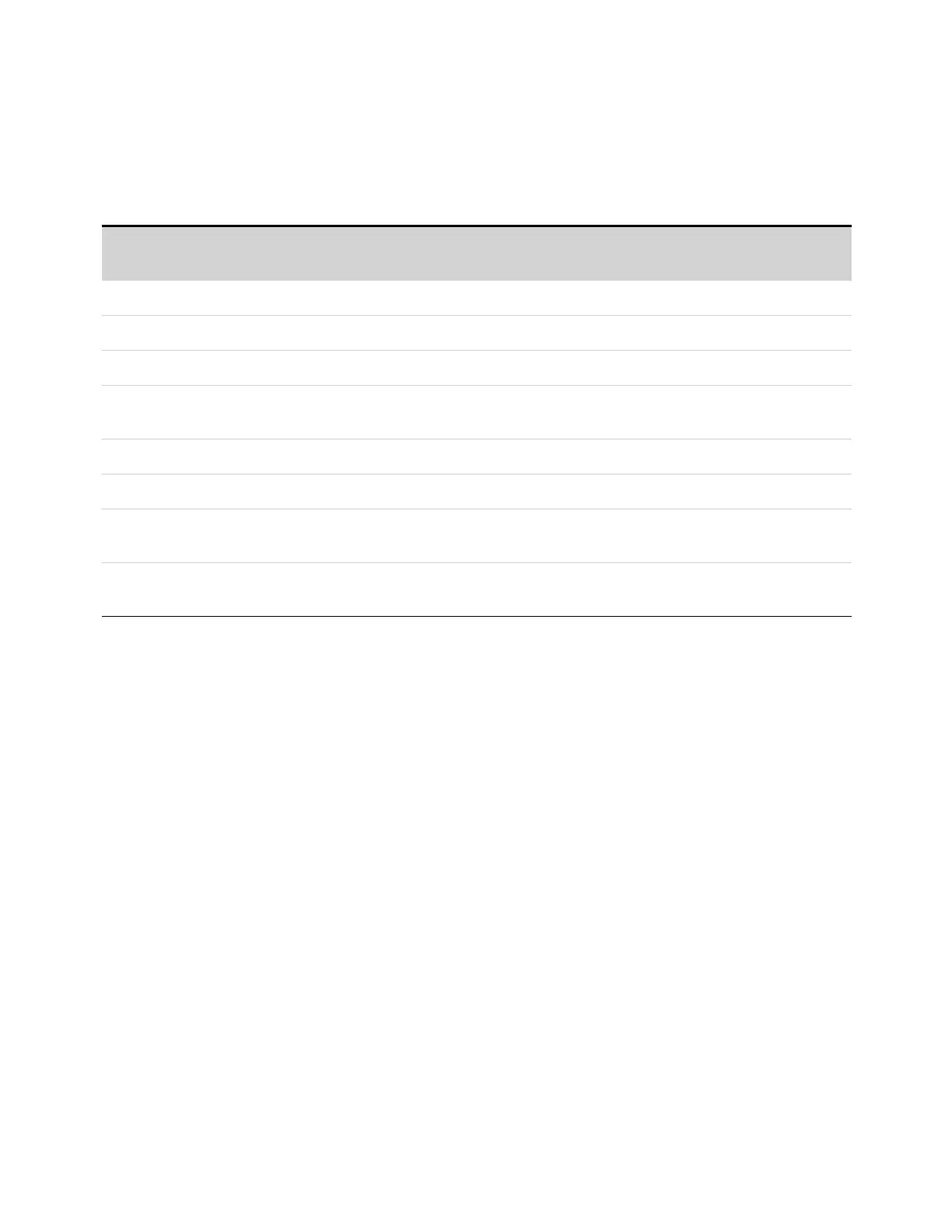

Status Byte Register

This register summarizes the information from all other status groups as defined in the IEEE 488.2

Standard Digital Interface for Programmable Instrumentation. The following table describes the

Status Byte register bit assignments.

Bit Bit Name Decimal

Value

Definition

0 not used not used 0 is returned

1 not used not used 0 is returned

2 Error Queue 4 One or more errors in the Error Queue. Use SYSTem:ERRor? to read and delete errors.

3 Questionable Status Sum-

mary

8 One or more bits are setin the Questionable Data Register. Bits must be enabled, see

STATus:QUEStionable:ENABle.

4 Message Available 16 Data is available in the instrument's output buffer.

5 Event Status Summary 32 One or more bits are setin the Standard Event Register. Bits must be enabled, see*ESE.

6 Master Status Summary 64 One or more bits are setin the Status ByteRegister and may generatea Request for Ser-

vice. Bits must be enabled, see *SRE.

7 Operation Status Sum-

mary

128 One or more bits are setin the Operation Status Register. Bits must be enabled, see

STATus:OPERation:ENABle.

Master Status Summary and Request for Service Bits

MSS is a real-time (unlatched) summary of all Status Byte register bits that are enabled by the Service

Request Enable register. MSS is set whenever the instrument has one or more reasons for requesting

service. *STB? reads the MSS in bit position 6 of the response but does not clear any of the bits in the

Status Byte register.

The RQS bit is a latched version of the MSS bit. Whenever the instrument requests service, it sets the

SRQ interrupt line true and latches RQS into bit 6 of the Status Byte register. When the controller does

a serial poll, RQS is cleared inside the register and returned in bit position 6 of the response. The

remaining bits of the Status Byte register are not disturbed.

Error and Output Queues

The Error Queue is a first-in, first-out (FIFO) data register that stores numerical and textual description

of an error or event. Error messages are stored until they are read with SYSTem:ERRor? If the queue

overflows, the last error/event in the queue is replaced with error -350,"Queue overflow".

The Output Queue is a first-in, first-out (FIFO) data register that stores instrument-to-controller

messages until the controller reads them. Whenever the queue holds messages, it sets the MAV bit

(4) of the Status Byte register.

Keysight N6900/N7900 Series Operating and Service Guide 288

6 SCPI Programming Reference

Loading...

Loading...