Chapter 13:

Theory of Operations

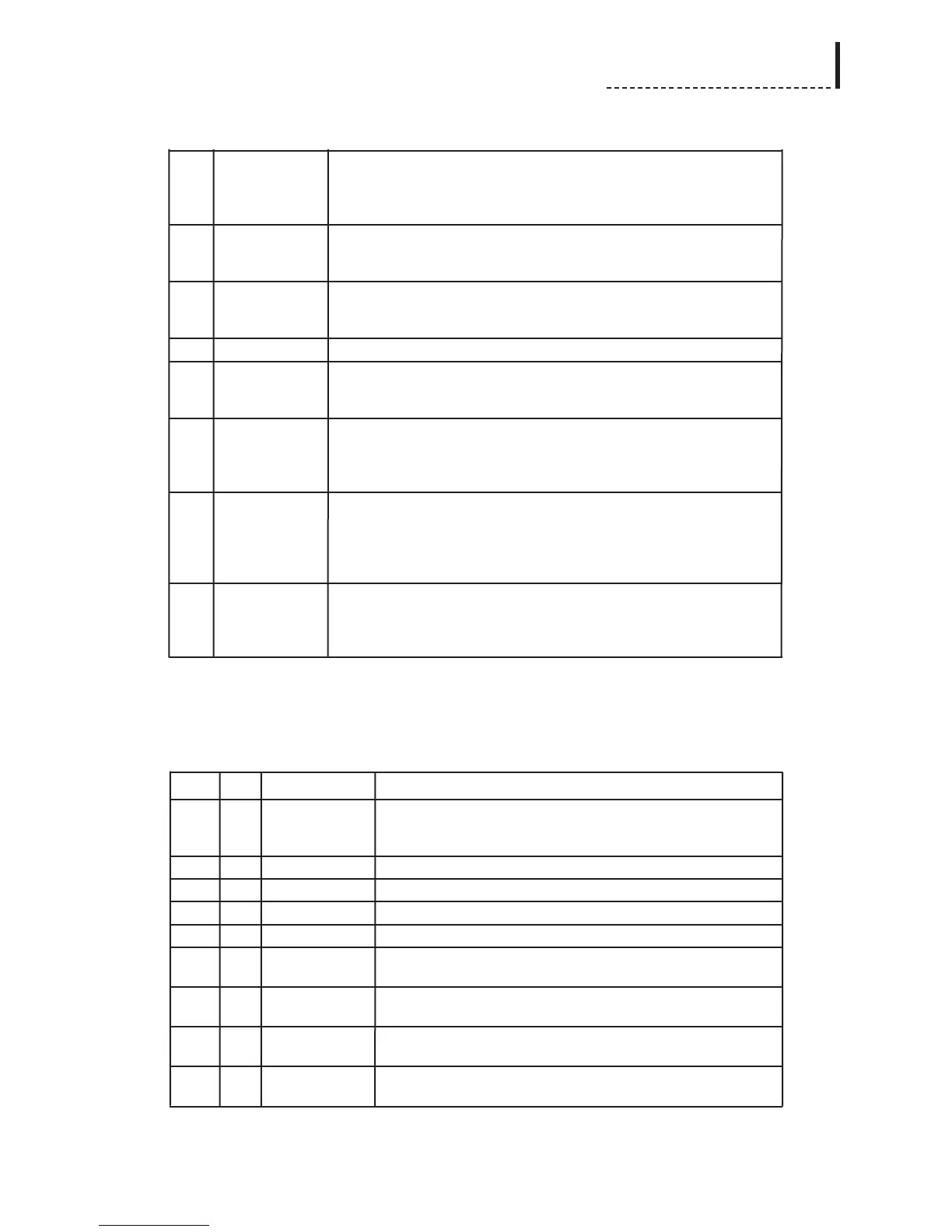

D7 CLOCK_OK The FPGA has waited sufficient time for the PLL to stabilise after a

sample rate change.

1 = Clock stable

0 = Continue to wait, clock not stable

D6 FPGA_DONE Used for configuring the FPGA

0 = Inactive

1 = Active; configuration complete

D5 FPGA_INIT Used for configuring the FPGA

1 = Inactive, initialisation complete

0 = Active; initialisation in progress or configuration error

D4 Unused - read 0

D3 SPI_ON The SPI interface has been activated

0 = SPI interface active

1 = SPI interface not active

D2 FPGA_JDOWN The FPGA download jumper is installed. The microprocessor does not

have control over the FPGA program port. This is an installation error

0 = Jumper installed

1 = Normal operation

D1 FPGA_JSER The FPGA serial program jumper is installed. Microprocessor must use

serial algorithm instead of parallel algorithm. This may be an

installation error.

0 = Normal operation

1 = Jumper installed.

D0 SPI_LSB This is the serial bit received from the addressed SPI device. May be

used to read back the SPI data.

0 = Low logic level

1 = High logic level

D11 through D8 are not used for the CPLD device.

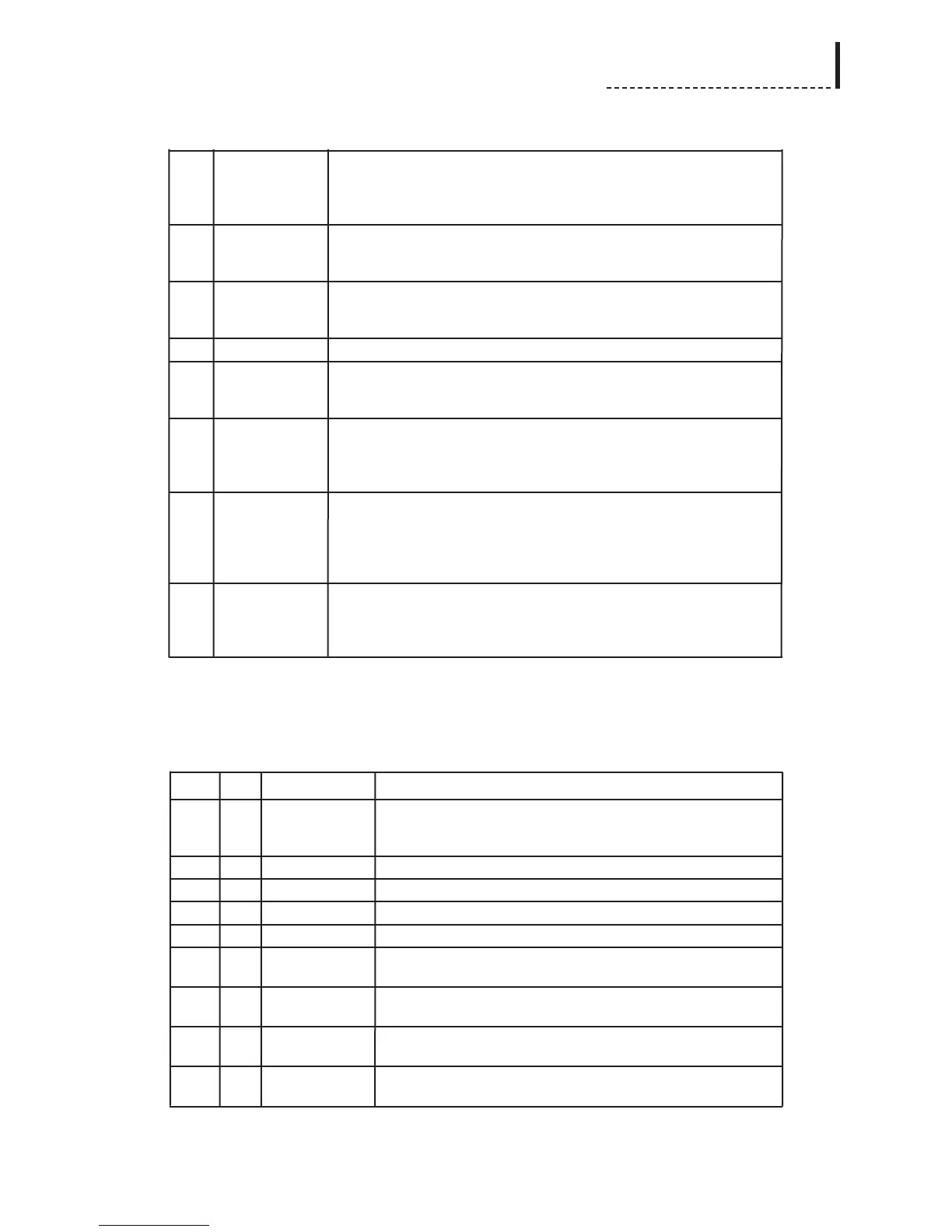

D15 through D12 are the control signals required by the card. All signals are read-

write accessible. The functions are defined according to the table:

A[2:0] Bit Name Comments

000 15 BYP_RLY4 Digital Channel 2 Bypass relay. Set to '1' to disable bypass (i.e.

channel active). The signal will be inhibited from going high

until the FPGA has been successfully programmed.

14 BYP_RLY3 Digital Channel 1 Bypass relay.

13 BYP_RLY2 Analog Channel 2 Bypass relay.

12 BYP_RLY1 Analog Channel 1 Bypass relay.

001 15 ANA_RLY4 Set the input mode for analog channel 2.

1 = balanced, 0 (default) = unbalanced

14 ANA_RLY3 Set the termination for analog channel 2.

1 = 600Ω, 0 (default) = high impedance (>20KΩ)

13 ANA_RLY2 Set the input mode for analog channel 1.

1 = balanced, 0 (default) = unbalanced

12 ANA_RLY1 Set the termination for analog channel 1.

1 = 600Ω, 0 (default) = high impedance (>20KΩ)

97

Loading...

Loading...