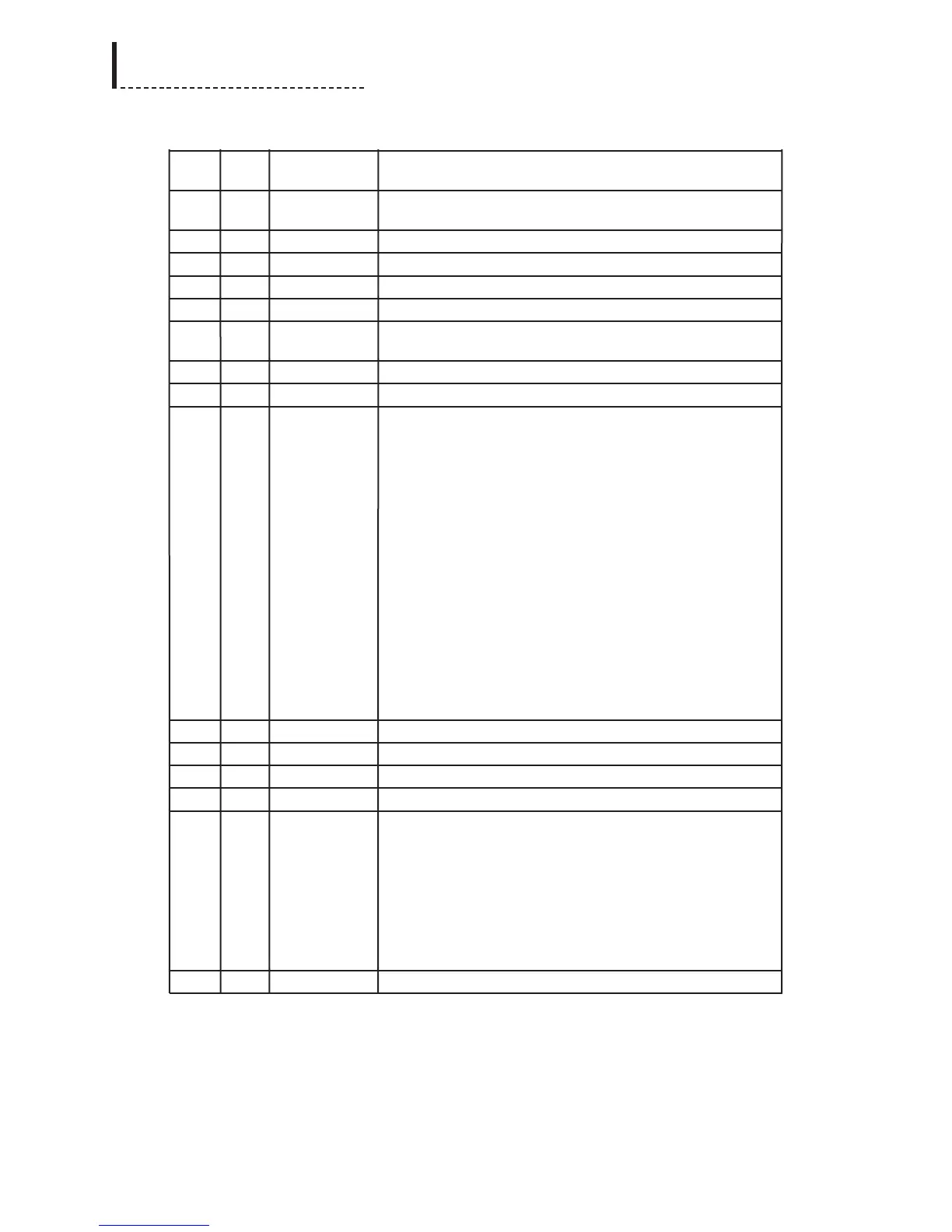

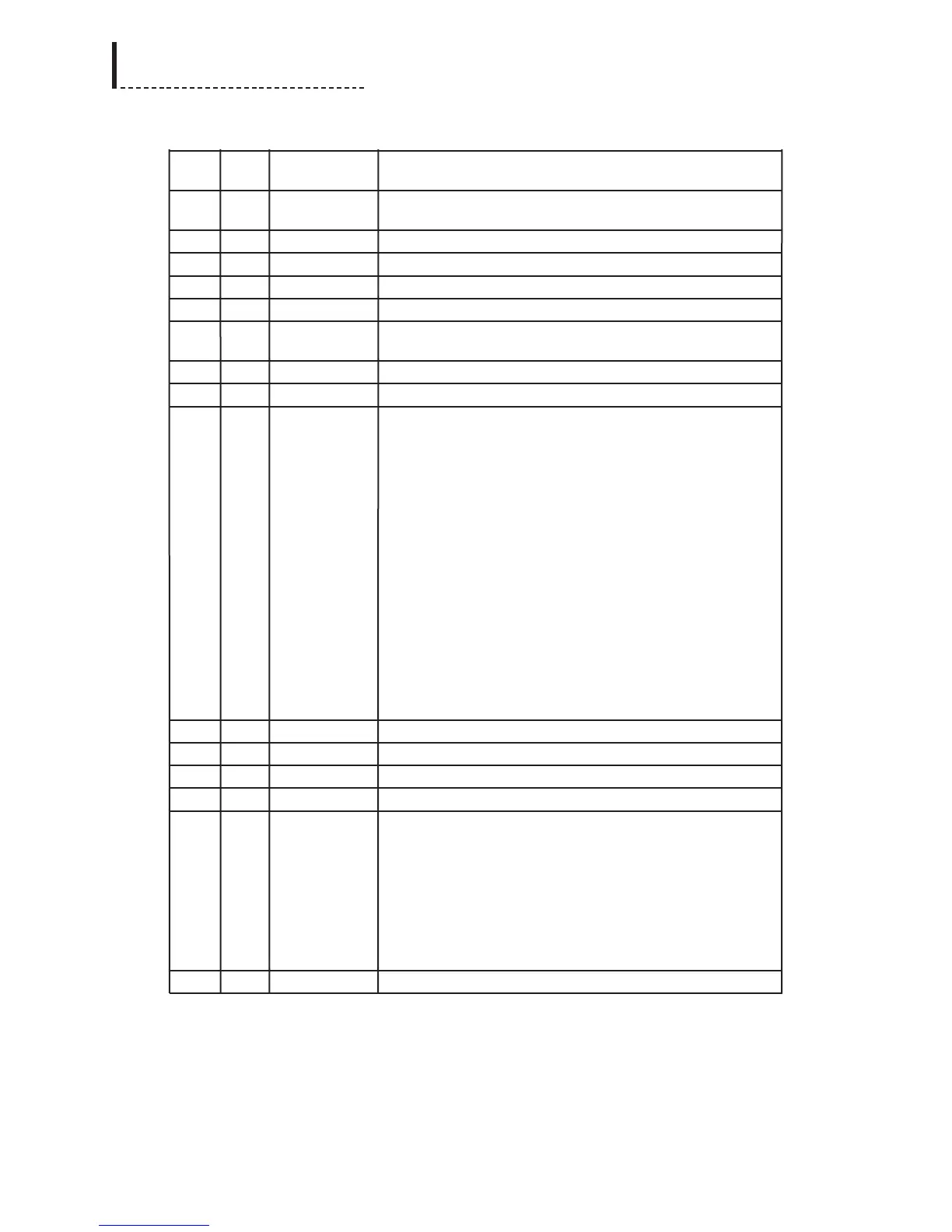

010 15 AES_BNC Select the digital input sources

1 = 75Ω unbalanced, 0 (default) = 110Ω balanced

14 SPDIF Select the digital output levels for the BNC:

1 = SPDIF, 0 (default) = AES Consumer

13:12 <not used>

011 15 FPGA_PROG Puts the FPGA into program mode.

14 FPGA_RST Resets the FPGA after configuration.

13 FPGA_WR Forces the FPGA Write signal active when set. This should

only be used during FPGA programming.

12 <not used>

100 15:13 SPI_SEL Select the active SPI device.

000: Variable Rate SRC, Stream 1

001: Variable Rate SRC, Stream 2

010: Digital Transceiver SRC, Channel 1

011: Digital Transceiver SRC, Channel 2

100: Digital Gain Control, Channel 1

101: Digital Gain Control, Channel 2

110: Analog CODEC, Channel 1

111: Analog CODEC, Channel 2

Writes to this register will set the SPI_ON control signal.

Reads to this register will not affect the SPI_ON control signal.

Reads or writes to any other register except register 7

(SPI_PORTAL) will clear the SPI_ON control signal. The

microprocessor must access some other register (such as

unused registers 5 or 6) to terminate the SPI transfer.If the

CLOCK_OK status signal is not active, then the SPI_ON

signal will not be activated.

12 <not used>

101:110 15:12 <not used>

111 15 SPI_PORTAL This is the bit that is written to the SPI serial line. It is

suggested that the microprocessor read a word of data, then

repeatedly write the word to register 7, followed by a left-shift,

until all bits of the word have been shifted out (16 cycles).

This method should make SPI accesses reasonably fast.

NOTE: The microprocessor must allow at least six 27MHz

clock cycles between successive writes to the SPI portal.

Probably the software will generate more than this time

through inherent delays.

14:12 <not used>

Prior to the FPGA programming, the "CLOCK_OK" signal will be inactive (low).

During this condition, neither the SPI register nor the bypass relay register will be

available. Attempting to write to the bypass relay register will cause all the bypass

relays to open, meaning all channels are in bypass mode. The SPI register will write

as usual, but the SPI_ON signal will not become active.

To program the FPGA, set the FPGA_PROG signal as described above. Ensure that

neither of the FPGA jumpers are installed. Write a byte of program data into D[7:0]

98

DPS-475/575 Service Manual

Loading...

Loading...