.

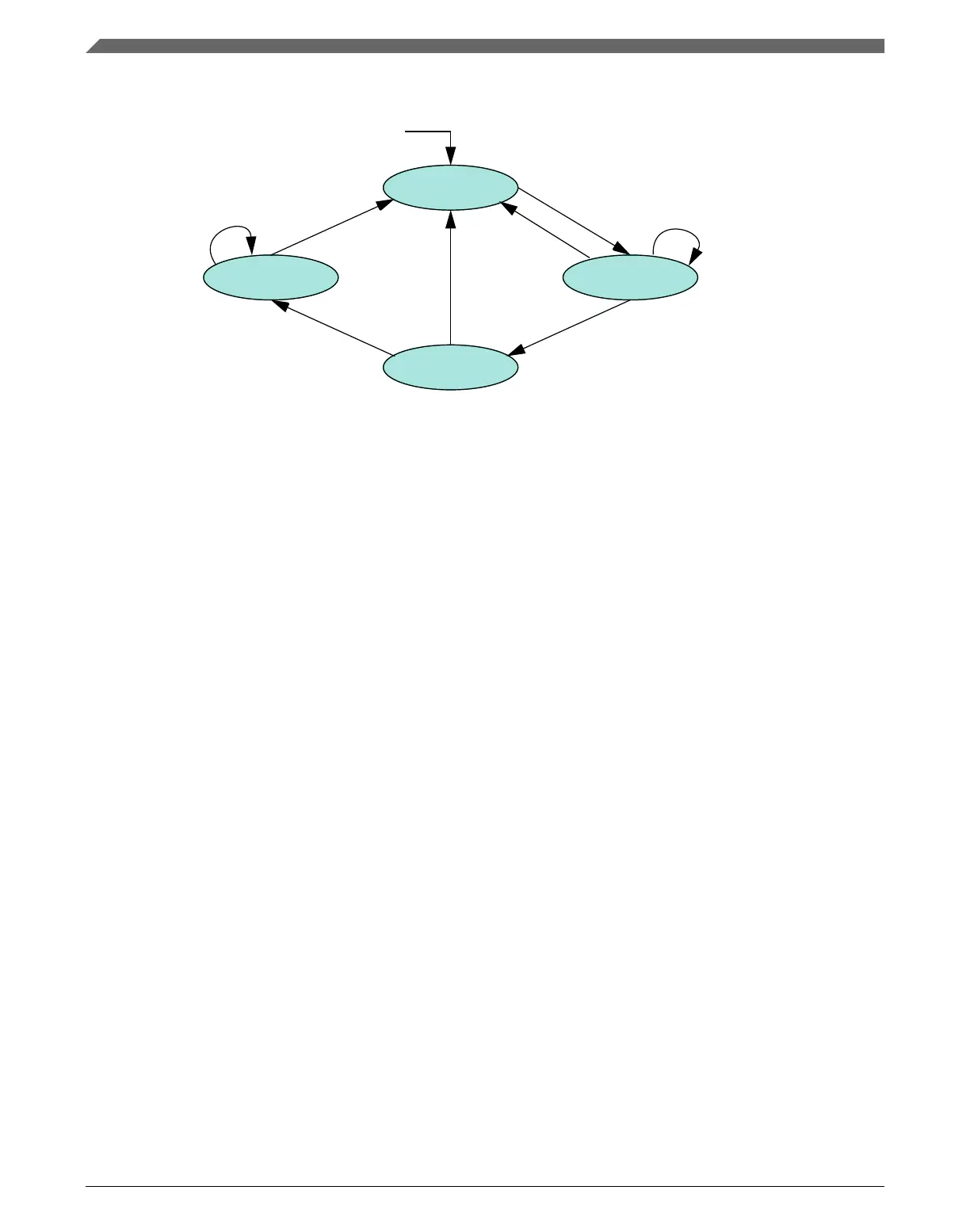

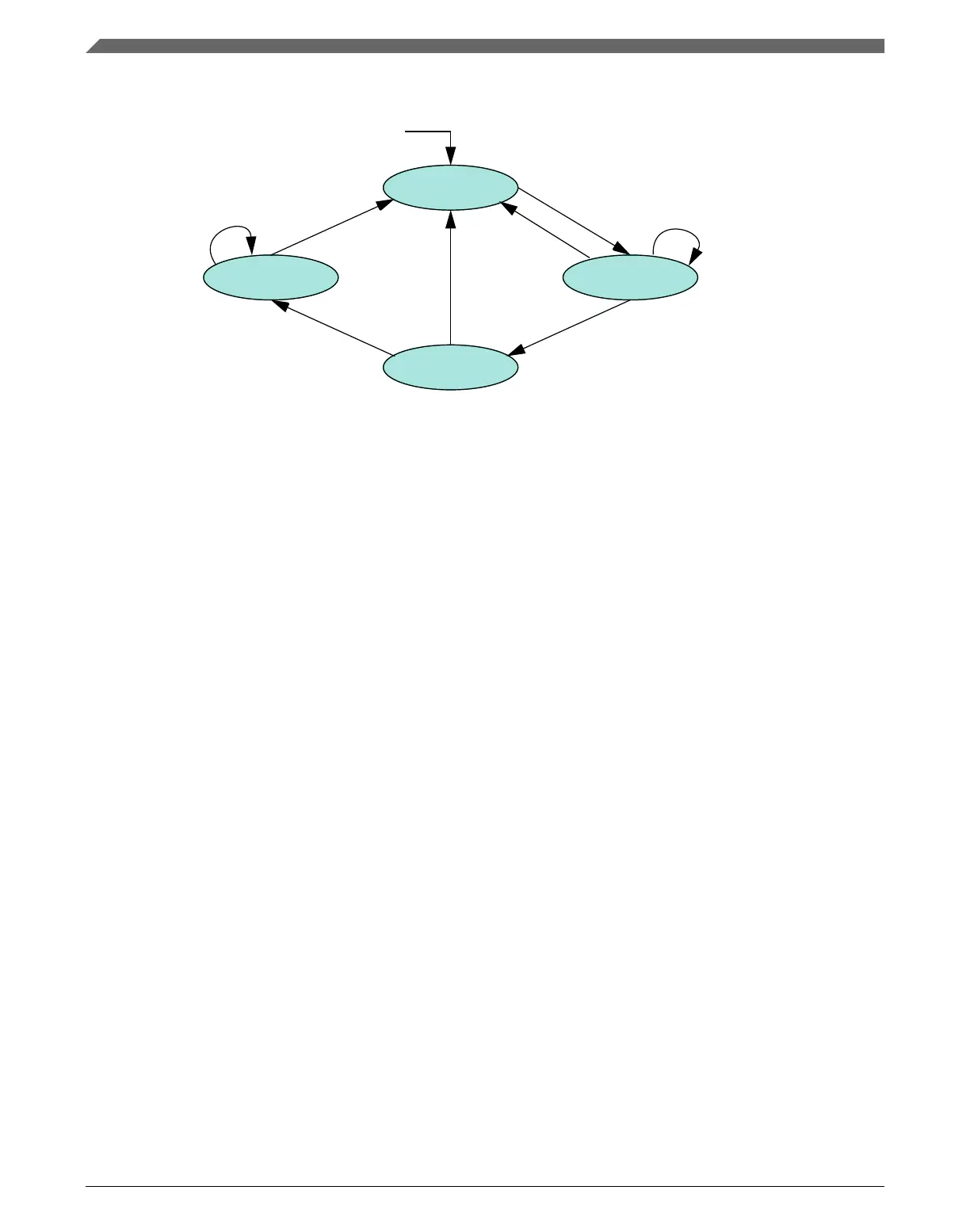

HW reset or

Init state

T0

DMS = 01

DMS = 00

DMS = 11

T2

DMS = 10

T3

T4

T5

T6

T7

T1

T8

Figure 3-57. Debug Message Handling State Machine

T0: reset m_can_dma_req output, enable reception of debug messages A, B, and C

T1: reception of debug message A

T2: reception of debug message A

T3: reception of debug message C

T4: reception of debug message B

T5: reception of debug messages A, B

T6: reception of debug message C

T7: DMA transfer completed

T8: reception of debug message A,B,C (message rejected)

3.5.5 Tx Handling

The Tx Handler handles transmission requests for the dedicated Tx Buffers, the Tx FIFO,

and the Tx Queue. It controls the transfer of transmit messages to the CAN Core, the Put

and Get Indices, and the Tx Event FIFO. Up to 32 Tx Buffers can be set up for message

transmission. The Tx Buffer element is described in Tx Buffer Element.

Note

AUTOSAR requires at least three Tx Queue Buffers and

support of transmit cancellation.

Functional Description

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

108 Freescale Semiconductor, Inc.

Loading...

Loading...